V850 - V850

| Obecná informace | |

|---|---|

| Spuštěno | 1994 |

| Přerušeno | proud |

| Společný výrobce |

|

| Výkon | |

| Max. procesor rychlost hodin | 32 kHz až 320 MHz |

| Šířka dat | 32 |

| Šířka adresy | 32 |

| Mezipaměti | |

| L1 mezipaměti | konfigurovatelný |

| Architektura a klasifikace | |

| aplikace | Vestavěné, Mobilní zařízení, Klimatizace, Automobilový průmysl |

| Min. velikost funkce | 0,8 μm až 40 nm |

| Mikroarchitektura | V810 (1991), V850 (1994), V850E (1996), V850E1 (1999), V850ES (2002), V850E2 (2004), V850E1F (2005), V850E2v2 (OPRAVIT MĚ), V850E2v3 (2009), V850E2v4 (2010), V850E2v3S (2011), V850E3v5 (2014) |

| Sada instrukcí | Řada V800 |

| Instrukce | v850: 74 v850e: 81 v850e1: 80 (83) v850e1f: 96 v850e2: 89 v850e2v3: 98 V850e3v5: OPRAVIT MĚ |

| Rozšíření |

|

| Fyzické specifikace | |

| Jádra |

|

| Produkty, modely, varianty | |

| Název (názvy) kódu produktu |

|

| Varianty | Rodina V850, Rodina RH850 |

| Dějiny | |

| Předchůdce | Jádro CISC „V80“ |

Tento článek je Použití externí odkazy nemusí dodržovat zásady nebo pokyny Wikipedie. (Srpna 2020) (Zjistěte, jak a kdy odstranit tuto zprávu šablony) |

V850 je ochranná známka název pro 32bitovou verzi RISC Architektura CPU z Renesas Electronics pro vložený mikrokontroléry, představený počátkem 90. let 20. století NEC a stále se vyvíjí od roku 2018.

Mnoho modelů V850 se vyvinulo mikroarchitektura rozšíření do dneška, ale všechny rozšíření mají binární kód úroveň zpětná kompatibilita z programy přes čtvrt století. Jeho základ je 32 z 32bitových univerzální registry s načíst / uložit architekturu. Má vysokou účinnost kódu, protože většina často používaných instrukcí je mapována do 16bitového půl slova.

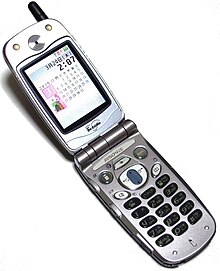

Ve své dřívější fázi se zaměřoval hlavně na ultranízké hodnoty spotřeba energie například 0,5 mW /MIPS. V850 byl široce používán v různých aplikacích, včetně: optické diskové jednotky, pevné disky, mobilní telefony, audio do auta a invertorové kompresory pro klimatizace. Ale dnes jsou nové mikroarchitektury zaměřeny hlavně na vysoký výkon a vysokou spolehlivost jako např dual-lockstep redundantní mechanismus pro automobilový průmysl. V dnešní době jsou řady V850 a RH850 komplexně používány v automobilech.

Přehled

V850 je ochranná známka název pro 32bitovou verzi RISC Architektura CPU pro vložený mikrokontroléry z Renesas Electronics Corporation. Původně byl vyvinut a vyroben společností NEC Corporation na počátku 90. let[1][2](autorská práva značka pro mikrokód na balík ukazuje © 1991) jako větev řady V800[3]:97, PDF 103a stále se vyvíjí dodnes.[4]

Jeho základnaarchitektura je následován Rodina V850 varianty pojmenované V850E, V850E1, V850ES,[5]V850E1F, V850E2, V850E2M, V850E2S a Rodina RH850 (V850E2M, V850E2S a V850E3) jádra CPU.

Mnoho překladačů a debuggerů je k dispozici od různých vývojový nástroj prodejci.

Operační systémy v reálném čase jsou poskytovány prodejci překladačů.

Emulátory v obvodu (ICE) poskytuje mnoho dodavatelů. Starší verze typu dokázaného podu, JTAG k dispozici je rozhraní N-Wire s typem N-trace a rozhraní Nexus s typem Aurora Trace.

Aplikační systémy

První V850 Pro mnoho bylo použito jádro CPU DVD mechaniky vyrobeno NEC Corporation, pak Sony Optiarc.[6][7]NEC Electronics (v současné době Renesas Electronics ) se intenzivně rozvíjí aplikačně specifické standardní produkty (ASSP) pro optické diskové jednotky pojmenovaný Řada SCOMBO®.[8][9]Tato první generace procesorového jádra byla také použita pro pevný disk disky vyráběné společností Quantum Corporation (viz foto).

The V850 / xxn produktová řada, začala s V850 / SA1[10]a V850 / SV1[11]rozšířila svou aplikaci na produkty ultra-lo-power, jako například „handy“ videokamery "Má hlavní a dílčí vnitřní oscilátor zesilovač pracuje od 1,8 V do 3,6 V s externím rezonátor, jako krystal a keramický.[10]Softwarový režim STOP, který interní časovač hodinek pracuje s 32,768 kHz sub-oscilátorem, spotřebuje obvykle 8 μA elektrický proud pouze.[12][13]NEC také zahájila V850 / SB1[14]pro audio do auta s IEBus v roce 1998, což je ultra nízký výkon (3,6 mW @ 5 V / MIPS) a ultra nízká hlučnost (EMI / EMS) 5 V produkt.[15]A V850 / SC1[16]byl také pro "audio do auta".[17]Tato strategická expanze produktové řady dokázala úspěšně zvýšit počet prodaných zařízení.

Tato první generace jádra V850 se používá také pro některé mobilní telefony NEC.[18]Používá se také pro programovatelné hostitelské CPU některých malých tvarový faktor "GSM /GPRS s GPS "vloženo modem moduly.[19]

V další fázi se NEC zaměřila na automobilový průmysl s Sběrnice CAN řadič na V850[20]tak jako V850 / SF1 nakonec.[21]Automobilový průmysl se později stal hlavním cílem modelů V850 a RH850.

The V850E základní SoC i standardní produkty,[22][23]používá se pro některé japonské domácnosti mobilní telefony, počítaje v to Sony Mobile a NEC.[24][25][26][27][28]V850E a V850ES se také používají pro klimatizace invertorové kompresory.[29][30][31][32]V této fázi byl jedním z masových trhů automobilové audio.[33]The V850ES jádro uspělo s nízkou spotřebou zabudované produktové řady,[34]který je JE kompatibilní s V850E.NEC Electronics (v současné době Renesas Electronics) adoptuje jádro procesoru V850 pro své „USB 3.0 "řadiče.[35]:11

Kolem roku 2005, studie proveditelnosti pro "FlexRay „řadič na platformě V850E byl spuštěn v několika společnostech. Společnost Yokogawa Digital Computer (v současné době DTS INSIGHT) vyvinula hodnotící desku s názvem GT200; s V850E / IA1 a FPGA, který zaměstnává „FlexRay "řadič vyvinutý společností Bosch.[36]:78, PDF80

The V850E2 hlavní primární cílené automobilové oblasti,[37]ale byl také použit pro NEC mobilní telefony.[38]

Aktuální sestava rodiny V850 (včetně rodiny Renesas RH850 na základě V850E3 Core, as of 2018) pokrývá hlavně automobilové aplikace a také MCU specifické pro „propojení mezi zařízeními“ a „řízení motoru“. Rodina V850 (založená na V850E, V850ES, a V850E2 jádra) a rodina RH850 (na základě V850E3 core, as of 2018) are used in automotive industry komplexly.[39][40]

Strategie ochranných známek

V850 je a ochranná známka ale ne registrovaná ochranná známka.[41]NEC jej jednou aplikoval na Japonský patentový úřad, ale byla zamítnuta pro registraci,[42][43]protože se jednalo o přirozené rozšíření čísla série. Ale tato akce má dostatečný účinek, aby zabránila jiným lidem nebo organizacím zaregistrovat ji jako ochrannou známku. Kromě toho společnost Renesas (dříve NEC) používá ochrannou známku typu V850X / xxn, jako je V850E / MA1, již více než 20 let, protože jako „registrovaná“ ochranná známka nelze udělit kombinaci 1 abecedy se 2 číselnými řetězci. Je tedy zdarma k použití bez jakékoli registrace a nikdo za to nemůže.

Jedna výjimka je V850E / PHO3 (PHOENIX 3 nebo PHOENIX-FS).[44]:3[45]:33Další použití PHOENIX 3 společnosti Renesas Electronics je COOL PHOENIX 3, který zaměstnává ARM Cortex-M0 jádro.[46]Mimochodem, „PHOENIX 3®“ je registrovaná ochranná známka společnosti Společnost 3DO tak jako USPTO Reg. 2 009 119.[47]

Podle aktuální dokumentace společnosti Renesas Electronics jsou jako její ochranná známka vyžadovány alespoň následující řetězce. „Řada V800,“ „Rodina V850,“ „V850 / SA1,“ „V850 / SB1,“ „V850 / SB2,“ „V850 / SF1,“ „V850 / SV1,“ „V850E / MA1,“ „V850E / MA2 , "" V850E / IA1, "" V850E / IA2, "" V850E / MS1, "" V850E / MS2, "" V851, "" V852, "" V853, "" V854, "" V850, "" V850E, " a „V850ES.“[41][48]

Protože ochranná známka V850 se používá již více než 20 let, většina lidí neví, že rodina RH850 je založena na rozšíření V850 architektura sady instrukcí a je zpětně kompatibilní s modely V850, V850E, V850ES a V850E2. RH850 je považován za novou tvář bez velkých starších softwarových aktiv V850.[49][50]

Architektura

Základní architektura

Základ V810 a V850 je typický univerzální registry -na základě načíst / uložit architekturu.[51]:4Mají 32 32bitových registrů pro všeobecné účely a R0 je opraveno jako Nulový registr který obsahuje vždy nulu. Ve verzi V850 je implicitně používán R30 SLD / SST; 16bitový krátký formát načtení / uložení pokynů jako ukazatel na prvek (ep),který režim adresování obsahuje základní registr adres ep a okamžitá vyrovnání operandů. V V850E nebo novější mikroarchitektury, R3 také implicitně používá PŘÍPRAVA / LIKVIDACE; zásobník volání pokyny pro vytváření a odvíjení rámů, jako ukazatel zásobníku. Překladače konvence volání také používá R3 jako ukazatel zásobníku.

Originální V850 má jednoduché 5stupňové 1hodinové hřiště potrubí architektura.[48]:114–126To jsou významné rysy RISC; počítače se sníženým počtem instrukcí. Ale velikost objektového kódu je asi poloviční oproti MIPS R3000.[51]:5 protože V810 a V850 přijaly 16bitový a 32bitový 2pásmový formát instrukce délky formuláře,[48]:38–40[51]:17[52]:29–30a většina často používaných instrukcí je mapována do 16bitového půl slova. Jinými slovy, 16bitová šířka externí sběrnice je relativně dost na to, aby poskytovala pokyny nepřetržitě bez zablokování potrubí, což umožňuje nízkou spotřebu energie na aplikační desce a je vhodná pro mobilní zařízení. Tento koncept je podobný Renesas (dříve Hitachi) SH, ARM palec, a MIPS16 architektury instrukční sady.[53]:4

Kromě toho provádění instrukční sada je opatrně vybrán. Například, volání funkce s Přejít a (zaregistrovat) odkaz návod,[48]:61[51]:20[52]:64 které uloží další PC v registru (ve verzi V810 fixovaný na R31), je také jedním z RISC technika ke snížení počtu pokynů. Návrat z funkce lze provést pomocí jmp [Rn] (jmp [R31] ve verzi V810).[48]:61[51]:23[52]:65 Typický Procesory CISC použití zavolat a vrátit se pokyny a zatlačte na další PC na jejich zásobníková paměť plocha.

Ale V810 a V850 nějaké mají mikroarchitektura rozdíly. V810 přijímá provoz mikroprogramu metoda pro některé pokyny; aritmetika s plovoucí desetinnou čárkou a bitový řetězec provoz, zatímco V850 je stoprocentní drátové ovládání metoda. Jako výsledek například první V850 nemá aritmetika s plovoucí desetinnou čárkou a sady instrukcí bitové manipulace; včetně "find first one / zero" (hledat 1/0; SCH1x / SCH0x), kromě „set / clr / negate a bit“ (SET1 / CLR1 / NOT1). Tyto rozšířené instrukční sady jsou oživeny v rozšířeních V850E2x.

Ačkoli řada V800 přijímá RISC architektura sady instrukcí, jejich montážní jazyk je ruční kódování přátelský. Přijímají přímo vpřed načíst / uložit architekturu.[51]:4 Kromě toho „blokovat "mechanismus pro datová rizika a pro nebezpečí větví jsou implementovány,[51]:33–35 jinými slovy, montážní jazyk programátor nemusí uvažovat o žádném zpoždění sloty. Flexibilitu poskytuje 32 univerzálních registrů montážní jazyk uživatelů. Směs ručně sestavených kódů a kompilovaných kódů v jazyce C je k dispozici pomocí možností kompilátoru, například „-mno-app-regs“ v Sbírka kompilátorů GNU.[54]

Je to trochu škoda V instrukce V810 je odstraněna z první V850, což umožňuje nepodepsané načtení z paměťově mapované I / O.[51]:22[52]:63

Podrobná diskuse je k dispozici v některých starých časopisech.[55][56]

Hlavním účelem úpravy V810 na V850 je aritmetika nasycení z důvodu požadavku zákazníkůpožadavek zákazníků[Citace je zapotřebí ].

Rozšíření mikroarchitektury

Řada V850 opakovala mnoho mikroarchitektura rozšíření, ale všechny rozšíření mají zpětná kompatibilita.[57]Jinými slovy, všechna stará binární softwarová aktiva, včetně těch, která byla napsána před čtvrt stoletím, fungují na každém novém jádru. mikroarchitektura má během čtvrt století varianty implementace obvodů a varianty technologie výrobního procesu.

V roce 1996 byl V853 oznámen jako první 32bitový RISC mikrokontrolér s integrovaným flash paměť.[58]Ale jeho maximální počet cyklů „mazání a zápisu“ byl 16 počtů.[59]:37

V roce 1998 NEC strategicky zahájila rozšiřování produktové řady V850 v obou zemích standardní a ASSP podnikání a v ASIC a SoC podnikání.[60]

První generace modelu V850 nemá nepodepsaný instrukce k načtení, která byla odstraněna z V810 (jako IN.H a IN.B), poté byl přidán znovu jako LD.HU a LD.BU ve druhé generaci; Řada V850E (V850E1). Kromě toho má V850E některé další uživatelsky přívětivé CISCY rozšíření jako „tabulka volání“, „přepínač“ a „připravit / zlikvidovat“.[61]:217

V roce 2001 představila společnost NEC jádro V850ES, což je řada s velmi nízkým výkonem, ale je kompatibilní s ISA s V850E.[62]

Kolem roku 2001 se zdálo, že jádro Java Acceleration IP pro V850 je některým zákazníkům poskytováno jako SoC,[63]ale podrobné informace jsou uvedeny pouze v některých patentech.[64][65]

V roce 2005 představila společnost NEC Electronics jádro V850E2 jako produktovou řadu V850E2 / ME3 s superskalární architektura.[66]

V roce 2009 představila společnost NEC Electronics V850E2M jako dvoujádrový s 2,56 MIPS / MHz a 1,5 mW / MIPS.[67]

V roce 2011 společnost Renesas zveřejnila rozšíření SIMD pro V850 as V850E2H.[57][68]Pokud jde o rozšíření SIMD, byla provedena některá akademická studia.[69]Architektonická dokumentace k této nejnovější produktové řadě je ale zpřístupněna pouze zákazníkům v automobilovém průmyslu. Nelze jej najít na webových stránkách společnosti Renesas.[70]Název se zdá být změněn na V850E3 nebo G3H. Jediný způsob, jak vědět o jeho instrukční sadě, je udělat “reverzní inženýrství "z Sbírka překladačů GNU.

Spotřeba energie

Původní V810 a V850 Architektura CPU je určen pro aplikace s velmi nízkým výkonem.

Podrobný popis modelu V810 je popsán v některých časopisech.[71][72]

Podle dokumentace Renesas, spotřeba energie implementace V850ES / Jx3-L je přibližně 70% ARM Cortex-M3.[5]:14,15

V810 pracuje od 2,2 V do 5,5 V s výrobním procesem 5 V 0,8 μm (CZ4),[73]přičemž ztrátový výkon s Dhrystone MIPS je 500 mW s 15 MIPS a 40 mW s 6 MIPS při 5 V, respektive 2,2 V. Jedná se o jeden z 32bitových produktů s nízkou spotřebou mikrokontroléru na počátku 90. let. Této specifikace lze dosáhnout jak dobře zváženým architektura sady instrukcí a precizně naladěným 5stupňovým 1hodinovým hřištěm mikroarchitektura, oba jsou výhodou zjednodušeného RISC Vlastnosti.

Tato DNA s ultra nízkou spotřebou je nahrazena produktovou řadou V850 / Sxn, které jsou stále naživu v hromadné výrobě po více než 20 let. Většina z nich je vyráběna při 3,3 V s procesem výroby 0,35 μm (UC1), jehož jádro CPU je přesně vyladěno tak, aby fungovalo od 1,8 V do 3,6 V, pracuje na 32,768 kHz (sub-osc.) Až 16,78 MHz (main-osc. ) s interním oscilátor zesilovač plus externí rezonátor (krystal nebo keramický ).[10]Ztrátový výkon je 2,7 mW / MIPS pro 3,3 V 0,35 μm (UC1) výrobní proces a 3,6 mW / MIPS pro 5 V 0,35 μm (CZ6) výrobní proces. Pohotovostní režim „Software STOP“ pro masku ROM verze V850 / SA1, který interní časovač hodinek pracuje na 3,3 V s 32,768 kHz sub-oscilátorem (IDD6), spotřebuje obvykle 8 μA elektrický proud pouze. Normální provozní režim Subclock při 3,3 V s 32,768 kHz spotřebuje obvykle 40 μA, maximálně 140 μA. (JáDD5)[74]:440, IDD5[13]Jeho běžný provozní proud CPU 1,8 V při 32,768 kHz může být 22 μA (40 μA ÷ 3,3 V × 1,8 V), přičemž ztrátový výkon by měl být 40 μW. To odpovídá 1,0 mW / MIPS (40 μW ÷ 0,032768 MHz ÷ 1,15 DMIPS / MHz ÷ 1000).

Produktová řada V850 / Sxn je také vyladěna pro nízkou hlučnost EMI a s EMS. Zejména V850 / SB1 a SB2 jsou speciálně vyladěny pro nízký šum EMI s 5 V interním regulátorem napětí, který umožňuje vysokou citlivost příjmu RF pro autorádio.[75]:41–44

V roce 2011 zahájila společnost NEC 3. generaci mikroarchitektura Řada V850ES s velmi nízkým výkonem, která trvá 1,43 mW / MIPS v rozsahu provozního napětí od 2,2 V do 2,7 V,[62]ale tato první implementace mikroarchitektury V850ES se zdá být neúplná ve srovnání s pozdějšími generacemi stejné architektury. Jeho pohotovostní režim „Sub-IDLE“ pro masku ROM verze V850ES / SA2 a V850ES / SA3, tyto interní RTC pracují při 2,5 V s 32,768 kHz sub-oscilátorem (I.DD6), spotřebovávejte obvykle pouze 5 μA elektrického proudu. Normální provozní režim Subclock při 2,5 V s 32,768 kHz však obvykle spotřebuje 40 μA, maximálně 100 μA.[76]:509Jeho běžný provozní proud CPU 2,2 V při 32,768 kHz může být 31 μA (40 μA ÷ 2,5 V × 2,2 V), přičemž ztrátový výkon by měl být 68 μW. Jedná se o 1,7krát vyšší verzi než V850 / SA1. Odpovídá 1,6 mW / MIPS (68 μW ÷ 0,032768 MHz ÷ 1,3 DMIPS / MHz ÷ 1000).

Produktová řada V850ES / JG3-L má varianty s velmi nízkým výkonem, pojmenované μPD70F3792, 793 a μPD70F3841, 842. Mohou pracovat od 2,0 V do 3,6 V s typickým 18 μA elektrický proud při 32,768 kHz,[77]:1002, 1041 což by mělo být 22 μW při 2,0 V (18 μA × 2,0 V ÷ 3,3 V × 2,0 V). To odpovídá 0,52 mW / MIPS (22 μW ÷ 0,032768 MHz ÷ 1,3 DMIPS / MHz ÷ 1000). Kromě toho by jejich klidový režim dílčích hodin s časovačem hodinek, spotřeba energie měla být typicky 3,4 μW při 1,8 V (3,5 μA ÷ 3,3 V × 1,8 V × 1,8 V).[77]:1002, 1041

The spotřeba energie jádra NA85E2 (V850E2) je mnohem větší ve srovnání s jádrem NU85E (V850E1) ve stejném CB-12L (UX4L)[73][78]výrobní proces. Důvodem je, že jádro V850E2x má 128bitovou šířku prefetch instrukce autobus a množné číslo Fronty předběžného načítání instrukcí,[79]:16zatímco průměrná délka instrukcí řady V800 je téměř 16bitová.[51]:17To znamená, že z paměti je možné načíst 16 instrukcí najednou, poté paměť a obvody prefetcher odpočívají 3 až 7 cyklů pro dual-pipeline superskalární architektura. Tato mezera zvětšuje rozdíly amplitudy elektrického proudu a navíc špičku elektrický proud převyšuje příspěvek na stabilizátory napětí mobilních zařízení gadgety Pokud jde o jádro procesoru V850E2M, je veřejně představeno jako 1,5 mW / MIPS, 3krát oproti předchozím generacím, i když by mělo mít výhody nových technologie výrobních procesů.[67]Některá mobilní zařízení se vyhýbají použití duální instrukce (dual-pipeline superskalární ), jinými slovy, přijetí nastavení provádění jedné instrukce (single-pipeline) ke snížení rozdílů amplitud elektrického proudu.

Metodika rozvoje

Protože rodina V850[48]:16je vyvinut jako větev řady V800,[3]:97, PDF 103základní Architektura CPU je zděděno z V810.[81]Architektura instrukční sady první V850 je drasticky upravena oproti V810, ale rozdíl je v úrovni patche od Sbírka překladačů GNU úhel pohledu.[82] Hlavním účelem této změny je implementace aritmetika nasycení na přání zákazníka.

Podrobná metodologie návrhu V810 je popsána v časopise.[83]V850 využívá tento design. Ale datová cesta logika byla změněna z dynamická logika statická logika, povolit 32,768 kHz hodiny v reálném čase kmitočtový provozní režim.

The úroveň přenosu registru "Architektura CPU design "modelu V810 byl vyvinut s Jazyk popisu funkce (FDL)[84][85][86]na Falcon Simulator software, to jsou NEC interně CAD nástroje. Tato metodika je stejná jako u metod NEC V60.[87]Na konci 80. let 20. století Verilog HDL nezískal Cadence Design Systems dosud.[88]FDL byl používán až do poloviny dvacátých let 20. století a byl také používán pro vývoj NEC super-počítač; pojmenovaný Earth Simulator.[89]

Rozdíl oproti V60 spočívá v tom, že Kruhový diagram byl napsán s editor schémat, ne z Calma, ale z Mentor Graphics volala SÍŤ,[90]část Architekt designu produkt[91][92]na Počítač Apollo je pracovní stanice, což je nejdůležitější schematický editor V té chvíli.[93]Umožnilo generovat netlisty, jako EDIF a KOŘENÍ, pro JÁ PROTI program jako kadence Drákula produkty a NEC interně a Zycad netlist pro logická simulace. Později toto Kruhový diagram z SÍŤ se stal schopen generovat úroveň brány Verilog HDL netlist pro V850.

Většina úroveň přenosu registru FDL netlist byl přeložen do úroveň brány schematické ručně, protože logická syntéza v té chvíli ještě nemusí být praktické. FDL byl rozdělen na datová cesta a náhodná logika přesně. Pro datová cesta část, úroveň brány Kruhový diagram povoleno ručně opakováno umělecká díla. Na druhou stranu pro náhodná logika část, logická syntéza se pokusil použít pro generování úroveň brány schematické, ale bylo to asi 10% z celkového okruhu.

Navíc, formální ověření také ještě nemusí být praktické využití, což znamená plné regresní test podle dynamický logická simulace je požadováno pro úroveň brány netlist porovnat s RTL jeden. Pro úroveň brány logická simulace, NEC interně CAD pojmenovaný nástroj V-SIM se obvykle používá.[94]Ale někdy hardwarový emulátor, jako Zycad LE akcelerátor simulace,[95]se pro tento účel používá. (Viz :.[96]:13V tomto materiálu je výkon Zycad LE je ve srovnání s NEC HAL, ale počáteční desetiletí designu se liší.[97])

Tabulka opcode instrukcí

Každý operační kód (operační kód) stůl je z Uživatelská příručka: Architektura (odkazují na externí odkazy. ).

V810 (zastaralé)

- 1. mapa opcodes

- Všechny operační kód (operační kód) z drátové ovládání operace je uzavřena během prvních 16 bitů poloviční slovo, přesněji prvních 7 bitů z MSB. Hloubka 64 slov ROM struktura s větev tabulka podmínek je dostačující pro dekódovací hardware. Pokud je 16bitový literál operand je vyžadováno, nachází se ve druhém půlslově. Ovládání mikroprogramu operace; bitové řetězce a aritmetika s plovoucí desetinnou čárkou pokyny, jsou také umístěny ve druhém 16bitovém půlslově. Ve výsledku se všechny instrukce stanou 16bitovou a 32bitovou dvoucestnou délkou formuláře. Nepodepsaný formulář zatížení paměťově mapované I / O je implementován jako v návod. Aritmetický a logický instrukce nejsou úplně, ale relativně ortogonální.

- V810 nemá aritmetika nasycení instrukce, ale 1 další instrukce ve formátu II, jako např SAT který kontroluje příznaky (Přetékat, Podepsat, Nula, a Půl slova) a přepíše zadaný registr, může stačit jak pro podepsané, tak i bez znaménka a pro slovní a půlslovní aritmetické operace.

Bit [12:10]

[15:13, 9]000 001 010 011 100 101 110 111 Formát 000 X MOV PŘIDAT SUB CMP SHL SHR JMP SAR I (R, r) 001 X MUL DIV MULU DIVU NEBO A XOR NE 010 X MOV PŘIDAT SETF CMP SHL SHR SAR II (imm5, r) 011 X PAST RETI STŮJ LDSR STSR Bit str.

100 0

100 1Bcond III (disp9) BV BZ / BE BN (BS) BLT BNV BNZ / BNE BP (BNS) BGE BC / BL BNH BR BLE BNC / BNL BH NOP BGT 101 X MOVEA PŘIDAT JR JAL NEBO JÁ ANDI XORI MOVHI IV / V 110 X LD.B LD.H LD.W ST.B ST.H ST.W VI (disp16 [R], r) 111 X IN.B IN.H CAXI IN.W OUT.B OUT.H Plovák OUT.W VI / VII

- „NOP“ je alias „Non-BR“.

V850 (1. generace)

- 1. mapa opcodes

Bit [7:5]

[10:8]000 001 010 011 100 101 110 111 Formát 000 MOV NE DIVH JMP SATSUBR SATSUB SATADD MULH I (R, r) 001 NEBO XOR A TST SUBR SUB PŘIDAT CMP 010 MOV SATADD PŘIDAT CMP SHR SAR SHL MULH II (imm5, r) 011 SLD.B SST.B IV (disp7 [ep], r) 100 SLD.H SST.H IV (disp8 [ep], r) 101 Bit [0] SLD.W / SST.W Bit [3: 0] Bcond IV / III 110 PŘIDAT MOVEA MOVHI SATSUBI NEBO JÁ XORI ANDI MULHI VI (disp16 [R], r) 111 LD.B 2. mapa ST.B 2. mapa JARL Bit [15:14]

SET1 / NOT1

/ CLR1 / TST12. mapa

RozšířeníV / VII / VIII

- „NOP“ je alias „MOV R0, R0“.

- 2. mapa opcodes

Bit [23:21] 000 001 010 011 100 101 110 111 Formát [16] 1. mapa Bit [10: 5] = 111001 0 LD.H VII 1 ST.H VII [16] 1. mapa Bit [10: 5] = 111011 0 LD.W VII 1 ST.W VII [26:24] 1. mapa Bit [10: 5] = 111111 000 SETF LDSR STSR undef SHR SAR SHL undef IX (R, r) 001 PAST STŮJ RETI 1. mapa

Bit [15:13]

EI / DI

undefProtiprávní pokyny X 01X Protiprávní pokyny — 1XX Protiprávní pokyny —

V850E / E1 / ES

- 1. mapa opcodes

Bit [7:5]

[10:8]000 001 010 011 100 101 110 111 Formát 000 —† NE PŘEPÍNAČ JMP ZXB SXB ZXH SXH I (R, r0) MOV DBTRAP Bit [4]

SLD.BU

/SLD.HUSATSUBR SATSUB SATADD MULH I (R0, r31) / IV undef I (R0, r) / IV DIVH I (R, r) / IV 001 NEBO XOR A TST SUBR SUB PŘIDAT CMP I (R, r) 010 VOLEJTE PŘIDAT CMP SHR SAR SHL undef II (imm5, r0) MOV SATADD MULH II (imm5, r) 011 SLD.B SST.B IV (disp7 [ep], r) 100 SLD.H SST.H IV (disp8 [ep], r) 101 Bit [0] SLD.W / SST.W Bit [3: 0] Bcond IV / III (disp9) 110 PŘIDAT Bit [15:11]

MOV (r = 0)Bit [15:11]

LIKVIDACE (r = 0)NEBO JÁ XORI ANDI Bit [15:11]

undefVI (imm16, R, r)

/ VI (imm32, R)

/ XIIIMOVEA MOVHI STASUBI MULHI 111 LD.B 2. mapa ST.B 2. mapa Bit [15:14]

SET1 / NOT1

/ CLR1 / TST12. mapa VII (disp16 [R], r)

/ VIII (imm3, disp16 [R])

- †: „NOP“ je alias „MOV R0, R0“.

- 2. mapa opcodes

Bit [23:21]

[16, 26:24]000 001 010 011 100 101 110 111 Formát 1. mapa Bit [10: 5] = 111001 0 XXX LD.H VII (disp16 [R], r) 1 XXX ST.H 1. mapa Bit [10: 5] = 111011 0 XXX LD.W VII (disp16 [R], r) 1 XXX ST.W 1. mapa Bit [10: 5] = 111 10X 0 XXX 1. mapa Bit [15:11] JR (r = 0) / JARL (r ≠ 0) V (disp22) 1 XXX 1. mapa Bit [15:11] PŘIPRAVTE (r = 0) / LD.BU XIII / VII (disp16 [R], r) 1. mapa Bit [10: 5] = 111111 0 000 SETF LDSR STSR undef SHR SAR SHL Bit [18:17]

SET1 / NOT1

CLR1 / TST1IX (R, r)

IX (R, [r])0 001 PAST STŮJ Bit [18:17]

RETI / CTRET

/ DBRET

/undef1. mapa

Bit [15:11]

EI / DI

undefundef X 0 010 SASF Bit [17]

MUL (R, r, w)

/ MULU (R, r, w)Bit [17]

MUL (imm9, r, w)

/ MULU (imm9, r, w)Bit [17]

DIVH (R, r, w)

/ DIVHU (R, r, W)Bit [17]

DIV (R, r, w)

/ DIVU (R, r, w)IX (R, r)

/ XI (R, r, w)

/ XII (imm9, r, w)0 011 CMOV (imm5, r, w) CMOV (R, r, w) Bit [18:17]

BSW / BSH

HSW /undefundef Protiprávní pokyny XI (c, R, r, w)

/ XII (c, imm5, r, w)0 10X Protiprávní pokyny 1 XXX LD.HU VII (disp16 [R], r)

Seznam Řada V800 Jádra CPU

| Jádro CPU | Varianty produktu | Možnosti cílení GCC[98] | Poznámky |

|---|---|---|---|

| V810[1] (1991) | Rodina V810 (V810, V805 V820, V821[99]) | Vyžadovat opravu zpět.[82] K dispozici na Planet Virtual Boy. GCC s názvem gccVB. | Zastaralé výrobky. Nepodepsané a podepsané zatížení. μcoded plovák (singl )[100] 5stupňový plynovod.[101] 6,7 mW / MIPS (5 V produkt) |

| V810 (1997) | Rodina V830 (V830 - V832[102]) | totéž | Zastaralé výrobky. Špičkové produkty. Multimediální rozšíření. |

| V850 (1994) | Rodina V850 začala V851 - V852[103] V853,[58][104][105] V854 | žádný nebo -mv850 | Zastaralé výrobky. 5stupňový plynovod. 4,4 mW / MIPS (5 V produkt) |

| V850 (1997) | V850 / xxn (např. V850 / SA1) | žádný nebo -mv850 | Ne pro nový vývoj. Podepsané zatížení. 1,15 Dhrystone MIPS / MHz Produkty s velmi nízkou spotřebou. 3,6 mW / MIPS (5 V produkt) 2,7 mW / MIPS (produkt 3,3 V) 1,0 mW / MIPS (1,8 V sub-provoz.) |

| V850E (1996) | V850E / MS1,[106][107] V850E / MS2 | -mv850e | Ne pro nový vývoj. Nepodepsané a podepsané zatížení. 1,3 Dhrystone MIPS / MHz Standardní výrobky. |

| V850E1 (1999) | V850E / xxn (např. V850E / MA1[22]) Jádro SoB NB85E[108][109] Jádro SoC NU85E[108][109] (Nejlepší mobilní zařízení Sony a NEC.) | -mv850e1 nebo –mv850es | Nepodepsané a podepsané zatížení. N-Wire a N-Trace. Standardní výrobky. Produkty SoC. |

| V850ES (2002) | V850ES / xxn (-x) (např. V850ES / SA2) | -mv850es nebo –mv850e1 | Nepodepsané a podepsané zatížení. Produkty s velmi nízkou spotřebou. 1,43 mW / MIPS (produkt 2,5 V) 0,52 mW / MIPS (2,0 V sub-provoz.) Je požadován posun na V850E2S. |

| V850E1F (2005) | V850E / PH2, V850E / PH3 V850E / PHO3 | Vyžaduje se oprava (možná). | V / V plovák (jednoduchá přesnost). |

| V850E2 (2004) | V850E2 / ME3 NA85E2 SoC jádro[108][110] (NEC je dlouhotrvající buňka. Nastaví životnost = 2004—2012.) | -mv850e2 | Ne pro nový vývoj. Mnoho errata, ale stále naživu. Single insn. vykonávající. (Duální provedení errata.) 7stupňový plynovod. S / W float. Standardní produkty. Produkty SoC. |

| V850E2 (v2) () | V850E2 / xxn (např. FIX ME) Jádro SoB NB85E2[108][110][111] | -mv850e2 | Errata uklidila. Duální provádění instrukcí. 7stupňový plynovod. S / W float. Standardní produkty. Produkty SoC. |

| V850E2M (2009) G3 | V850E2 / xxn (např. V850E2 / FG4) RH850 / nxn | -mv850e2v3 a -msoft-float | S / W float. Duální provádění instrukcí. 7stupňový plynovod. 2,56 Dhrystone MIPS / MHz 1,5 mW / MIPS Podpora více CPU jádra. Ochrana paměti. |

| V850E2R (2010) G3R | V850E2 / xxn (např. V850E2 / MN4) RH850 / nxn | -mv850e2v3 | V / V plovák (dvojitá přesnost). Duální provádění instrukcí. 7stupňový plynovod. 2,56 Dhrystone MIPS / MHz Podpora více CPU jádra. Ochrana paměti. |

| V850E2S (2011) G3K | V850E2 / xxn (-x) (např. V850E2 / Jx4-L) (např. V850E2 / Fx4-L) RH850xnx | -mv850e2v3 a -msoft-float | S / W float. 5stupňový plynovod. 1,9 Dhrystone MIPS / MHz Podpora více CPU jádra. Ochrana paměti. Mimořádně nízký výkon. Standardní výrobky. Kompatibilní s kolíky V850ES / xxn Automobilové výrobky. Je požadován posun na RH850. |

| V850E2H (2010)[112] V850E3 (2014) G3M G3MH, G3KH | RH850 / xnx (např. RH850 / C1H) | -mv850e2v4 a –mloop nebo -mv850e3v5 a –mloop | Rozšíření SIMD. 64bitové vícenásobné načítání / ukládání. Prodloužení smyčky. V / V plovák (dvojitá přesnost). Ochrana paměti. Podpora více CPU jádra. Automobilové výrobky. |

[99][102][106][107][1][101][82][103][104][105][108][112]

SoC řešení

SoC IP jádra

V roce 1998 začala společnost NEC poskytovat V850 Family jako jádro ASIC pro rozšíření svého podnikání v ASIC.[113]Kromě toho bylo pojmenováno jak jádro procesoru V850E1 Nx85E[114][115]a pojmenované jádro procesoru V850E2 Nx85E2,[116]respektive se také používají k rozšíření svého standardního podnikání v oblasti produktů s metodikou návrhu ASIC.

Různé SoC využívají toto jádro. Například v roce 2003 Dotcast, Inc. použité jádro NU85E pro a set top box přijímač digitální vysílání dat na základě dNTSC (údaje v NTSC video[117]) metoda. Toto jádro je vymyslel s procesní technologií CB-10 0,25 μm, která využívá 5 vrstvený kov.[118]:9–10

The NA85E2C jádro, které je vyvinuto v 1,5 V 150 nm CB-12L (UX4L)[73][78]výrobní proces,má hodně errata (4 stránky v příloze v předběžném manuálu k architektuře,[119]:230–233plus 7 stránek další dokument o omezeních,[120]pokud je to uvedeno na webu). Zdá se však, že to není záležitost použití, protože se jedná o dlouhodobý produkt.

NEC také rozšířil jádro pro proces výroby 130 nm CB-130 (UX5)[73]IC na bázi buněk, ale je to nejasné.[121][122]

Synopsys Jakmile bylo oznámeno DesignWare® IP jádro pro V850E,[123] ale podpora zastaralá.[124]

| název | Jádro | Buněčná základna série | Napájení zásobování | Uzel/ Gate L. | Fab. proc. [73] | Frekvence MHz | Typ | LED | Dokumenty. |

|---|---|---|---|---|---|---|---|---|---|

| NA851C | V851 | CB-9VX | 3,3 V | 350 nm | UC1 | 33 | S periferním | [113][125] | |

| NA853C | V853 | CB-9VX | 3,3 V | 350 nm | UC1 | 33 | S periferním | [113][126] | |

| NA85E | V850E1 | CB-9VX | 3,3 V | 350 nm | UC1 | Hromadné jádro | [114] | ||

| NB85E | V850E1 | CB-9VX | 3,3 V | 350 nm | UC1 | 66 | Hromadné jádro | [127][128] | [113][115][129] |

| NB85ET | V850E1 | CB-9VX | 3,3 V | 350 nm | UC1 | 66 | w / Trace I / F | [127][128] | [113][129] |

| NB85E | V850E1 | CB-10 | 2,5 V | 250 nm | UC2 | 66 | Hromadné jádro | [127][128] | [129] |

| NB85ET | V850E1 | CB-10 | 2,5 V | 250 nm | UC2 | 66 | w / Trace I / F | [127][128] | [129] |

| NU85EA | V850E1 | CB-10VX | 2,5 V | 250 nm | UC2 | 100 | Hromadné jádro | [127][128] | [129][130][131][132] |

| NU85ET | V850E1 | CB-10VX | 2,5 V | 250 nm | UC2 | 100 | w / Trace I / F | [127][128] | [129][130][131][132] |

| NDU85ETV14 | V850E1 | CB-12L | 1,5 V | 150 nm / 130 nm | UX4L | w / Trace I / F | [127][128] | [129][130][131] | |

| NDU85ETVxx | V850E1 | CB-12M | 1,5 V | 150 nm / 130 nm | UX4M | w / Trace I / F | [127][128] | [129][130][132] | |

| NA85E2C | V850E2 | CB-12L | 1,5 V | 150 nm / 130 nm | UX4L | 200 | w / Trace I / F | [110][133] | [129][132] |

| NB85E2C | V850E2 | CB-12L | 1,5 V | 150 nm / 130 nm | UX4L | 200 | w / Trace I / F | [110][133] | [129][132] |

| V850E2x | CB-130L | 1,2 V | 130 nm / 95 nm | UX5L | |||||

| — | — | CB-90L | 1,2 V | 90 nm / | UX6L | Nahrazeno ARM946.[111] | |||

| Interní | V850E2x | UX6LF | 1,2 V | 90 nm / | UX6LF | Pouze pro vnitřní použití Renesas ??? | |||

| — | — | CB-65L | 1,2 V | 65 nm / | UX7L | Přeskočeno. Nahrazeno ARM1156.[111] | |||

| — | — | CB-55L | 1,2 V | 55 nm / 50 nm | UX7LS | Přeskočeno. Nahrazeno ARM Cortex-M3. | |||

| — | — | CB-40L | 1,1 V | 40 nm / 40 nm | UX8L | Nahrazeno ARM Cortex-M4. | |||

| Interní | V850E3 | RV40F | 1,1 V | 40 nm / 40 nm | RV40F | 320 | Pouze pro vnitřní použití Renesas ??? |

FPGA prototypové systémy pro SoC

Prototypování FPGA systémy pro jádra V850E1, V850E2 a V850E2M SoC byly intenzivně rozvíjeny k rozšíření SoC podnikání. Obsahovaly jádro procesoru V850 LSI (TEG†) deska a doplněk „FPGA“. Většina z SoC výrobky byly pro mobilní zařízení; protože ztráta výkonu původní řady V800 RISC architektura ve srovnání s CISC.[1][5][101] Je to stejná logika jako PAŽE (což znamená Acorn RISC Machine) architektura je široce používán pro mobilní gadgety.

† TEG: Skupina testovacích prvků

- Renesas (NEC): Microssp (2006)[111]

- Renesas (NEC): Hybridní emulátor (2007)[138]

- Renesas (NEC): PFESiP® EP1 Evaluation Board (2008)[139]

- Renesas (NEC): PFESiP® EP1 Evaluation Board Lite (2008)[140]

- Renesas (NEC): PFESiP® EP3 Evaluation Board (2010): jádro procesoru V850E2M, max. 266 MHz provoz[141]

Strategický zmatek

Kolem 2011–2014, Renesas Electronics intenzivně rozšířil produktovou řadu V850E2,[144][145]ale tato vysokorychlostní expanze přinesla mnoho zmatků. Například u některých produktů V850E2 / xxn již bylo od roku 2018 požadováno jejich nahrazení RH850 / xnx.[146]Může to být nebo nemusí být Program dlouhověkosti produktu (PLP) úhel pohledu.[147]

V roce 2012 navíc společnost Renesas začala intenzivně podporovat migraci z 10 let staré produktové řady V850ES / Jx3 na nově vyráběnou verzi V850E2 / Jx4, například pro Ethernet a USB,[148][149]ale novější produkty nejsou na jejich webových stránkách od roku 2018 uvedeny.[39]

V současné době společnost Renesas Electronics navrhuje „duální“ lockstep systém, ale jeho předchůdce NEC V60-V80 měl „více modulární“ lockstep mechanismus tzv FRM[150]buď s vrátit zpět „opakováním“ nebo pomocí roll-vpřed „výjimkou“ pro každou instrukci zjištěnou poruchu před více než 20 lety. Kromě toho NEC V60-V80 má množné číslo implementace Systém UNIX V vydání portového produktu, z nichž jedno je v reálném čase UNIX RX / UX-832[151](zde 832 znamená μPD70833 (V80), ne V832). Jeho multiprocesorová implementace se nazývá HOŘČICE (Multiprocesorový Unix pro vestavěné systémy v reálném čase), který pracuje maximálně na 8 procesorech současně a jejich mechanismus uzamčení byl dynamicky konfigurovatelný.[152]Kde jsou tyto technologie?

V roce 2001 oba NEC Corporation a Synopsys, Inc. oznámili, že souhlasili s propagací V850E jako DesignWare® IP jádra.[123][124]Ale od roku 2018 není V850E uveden v knihovnách DesignWare.[153]

Lucent Technologies a Texas Instruments jednou licencované jádro V850 a V850E SoC,[154][155][156][157]ale zařízení nelze najít.

Metrowerks kdysi vyvinut CodeWarrior překladač pro V850, který byl jedním z hlavních poskytovatelů překladačů pro V850 v roce 2006.[158]Ale kolem roku 2010 to po absorpci do roku přerušili Motorola polovodičový sektor v roce 1999, Freescale Semiconductor v roce 2003, v současné době NXP Semiconductors od roku 2015.

V roce 2006 společnost NEC nevykázala žádný plán pro rodinu V850 jako jádra SoC.[111] Jádro V850E2, vyvinuté v roce 2004, popisuje jako poslední jádro pro SoC. Místo toho společnost NEC představila ARM9 (rameno v5) a ARM11 (rameno v6), zejména pro mobilní zařízení. Toto podnikové rozhodnutí však náhle snížilo jak čistý zisk zařízení LSI, tak z důvodu licenčních poplatků za ARM, tak z důvodu cenové konkurence s jinými Poskytovatelé ARM SoC. Tržby z prodeje „celkových řešení V850“, jako jsou vývojové nástroje, OS v reálném čase, balíčky middlewaru a emulátory v obvodech, se také snížily. Počet prodaných zařízení V850 se také náhle snížil, protože v té době byli hlavními zákazníky jader V850E1 a V850E2 mobilní zařízení. V roce 2009 se společnost NEC Electronics spojila se společností Renesas Technology Corp.[159]

V roce 2008 oznámila společnost KMC (Kyoto Mictocomputer), která je jedním z hlavních a prvního poskytovatele obvodového emulátoru pro řadu V850. exeGCC aktualizace od Rel. 3 k Rel. 4,[160]ale z tohoto aktualizačního seznamu to vyloučilo V850, ačkoli byly nově přidány PowerPC a ARM v7. Vybral SH-4A a ARM v7 místo V850 a RH850[161]ačkoli to bylo úzce spolupracovalo s NEC a Renesas Electronics.[158]

Jádra CPU V850 běží uClinux,[162]ale 9. října 2008, Linuxové jádro podpora pro V850 byla odstraněna v revizi 2.6.27.,[163] protože NEC zastavil údržbu.[164][165][166]Osoba odpovědná za údržbu linuxového jádra V850 byla sloučením přesunuta z NEC do Renesas, ale jeho úkolem byl stále design kompilátoru a nikdy se nevrátil k linuxové údržbě jádra.[167]Toto podnikové rozhodnutí brání možnosti přenesení pro Android.[168]Pokud jde o podporu linuxového jádra od roku 2018, společnost Renesas Electronics se zaměřuje hlavně na procesory SH3 / SH4 a M32R.[169][170][171][172][173]

Zaměřte se na softwarová řešení

Knihovny

- Red Hat, Inc.: Newlib pro C. běhová knihovna (libc.a) a matematická literatura (libm.a)[174]

- C runtime spouštěcí rutina (crt0.S) pro nejnovější verzi v850e3v5 mikroarchitektura je k dispozici.[175][176][177]

- Micro Digital Inc .: GoFast® pro rychlou softwarovou knihovnu s pohyblivou řádovou čárkou NEC V85x[178]

- The Sbírka překladačů GNU: Software s plovoucí desetinnou čárkou[179]

- The Sbírka překladačů GNU: Desetinná plovoucí desetinná čárka (libdecnumber.a)[180]

Operační systémy

Operační systémy z V850 jsou většinou provoz v reálném čase vůči.

Některé operační systémy vyžadují Jednotka ochrany paměti (MPU) rozdělit úkoly (nebo vlákna ) výhradně pro spolehlivost a bezpečnostní důvody. V takových případech v850e2v3 (Gen.3) mikroarchitektura nebo vyšší jsou povinné.

Operační systém založený na ITRON v reálném čase

ITRON je otevřený standard specifikace OS v reálném čase (RTOS), která je v Japonsku významná. Jeho specifikace je definována pod vedením Ken Sakamura jako součást Projekt TRON. Počáteční písmeno Já znamená „průmyslový“. Protože ITRON specifikace definuje pouze rozhraní a kostru, každý prodejce má svůj vlastní vkus implementace.

- Renesas:

- Toppers Project: Otevřený zdroj TOPPERS / JSP

- A.I. Korporace: Toppers-Pro / xxx[186]

- Projekt T-Engine: Otevřený zdroj T-jádro podle TRON Fórum[187]

- eSOL: eT-jádro; Rozšířené T-jádro - RTOS pro vestavěné systémy[188][189]

- eT-jádro / kompaktní, eT-jádro / vestavěné, eT-jádro / POSIX

- Vícejádrové vydání eT-Kernel

- eCos: Otevřený zdroj operační systém v reálném čase

V reálném čase kompatibilní s AUTOSAR, OSEK / VDX

AUTOSAR je architektura otevřených systémů z operační systém pro automobilový průmysl. Jeho účelem je zavést standardizaci ECU; Elektronická řídicí jednotka pro automobilové motory. AUTOSAR je vzestupně kompatibilní specifikace OSEK / VDX, což je také a konsorcium název Německa založený v roce 1993.

V Japonsku byl tento výzkum zahájen v roce 2006 jako společný projekt JAIST a DENSO. Společnost Renesas Electronics se k tomuto projektu připojila v roce 2009.[190]Protože současné procesory RH850 a V850 jsou zaměřeny hlavně na automobilový průmysl, je jedním ze strategických produktů společnosti Renesas Electronics. Jeho dokumentace je však k dispozici pouze v japonštině, protože je jejím hlavním zákazníkem Toyota Motor Corporation.

- Renesas: RV850 (dokumenty jsou pouze v japonštině)[191]

- ETAS GmbH: RTA-OS RH850 / GHS,[192] RTA-OSEK V850E / GHS[193]

- Mentor Graphics (dříve Accelerated Technology, Inc.): Nucleus OSEK[194]

- HighTec EDV-Systeme GmbH: Bezpečnostní systém EB tresos[195]

- Toppers Project: Open source TOPPERS / AUTOSAR[196]

- eSOL: Profil eMCOS AUTOSAR[197]

Další OS v reálném čase

- eSOL:

- eMCOS; Škálovatelné RTOS, distribuované Microkernel Architektura, ne-hypervisor typ OS[202]

- MiSPO:

- NORTi Professional; OS v reálném čase + Zásobník TCP / IP + Simulátor[203]

- Mentor Graphics (dříve ATI, v současné době Siemens Business):

Linux

- 9. října 2008 Linuxové jádro podpora pro V850 byla odstraněna v revizi 2.6.27,[163] zabránění možnosti přenesení Android.[168]

Middleware balíčky

Rozličný middleware aplikační software jsou poskytovány od různých dodavatelů.

- Renesas: Ovládání paměťové karty SD[211]

Nástroje pro vývoj softwaru

Překladače a assemblery

Většina překladačů, oba pro rodinu V850; a pro rodinu RH850 jsou přesně stejný produkt a jsou rozšířeny JE cíle jsou řízeny pomocí „možností příkazového řádku“.[212][213]

Překladače pro modely V850 Fmily a RH850 zahrnují:

- The Sbírka překladačů GNU (jméno je stále v850 pro RH850)[214] vyvinuli oba:

- od „Red Hat, Inc. „(dříve“Řešení Cygnus ") jako součást Sada vývojářů GNUPro[215]

- "KMC (Kyoto Micro Computer)" jako součást exeGCC[158][216][217]

- „CyberTHOR Studios, Ltd.“: Předinstalované binární soubory zdarma lze stáhnout registrací.[218]

- Renesas:

- Balíček kompilátoru C pro rodinu V850[219]

- Kompilátor CA850 C. pro V850E1 a V850ES (v850e1 a / nebo v850es, aka Gen. 1)[220]

- Překladač CX C. pro V850E2M a V850E2S (v850e2v3, aka Gen. 3)

- Softwarový balíček pro V850 [SP850] pro V850E2 (v850e2 (v2), aka Gen. 2)[221]

- Balíček kompilátoru CC-RH C. pro G3, G3K (H), G3M (H)[222]

- Balíček kompilátoru C pro rodinu V850[219]

- GHS (Green Hills Software): Green Hills Optimizing Compilers[223][224]

- Wind River Systems: Diab Compiler[225][226]

- Systémy IAR: Vestavěný pracovní stůl[227]

- Altium Limited: Tasking®; RENESAS RH850 SOFTWARE DEVELOPMENT TOOLS[228]

- Metrowerks: CodeWarrior (zastaralé)[158]

Disassemblers

Usually, dis-assemblers are provided as a part of C compiler or assembler packages.

- např.)

- The GNU Binutils: objdump (v850-elf-objdump nebo v850-elf32-objdump)[233]

- Radare2: Radare2 je sada příkazový řádek programovací nástroje pro reverzní inženýrství.[234] Otevřený zdroj kód is available from GitHub úložiště.[235][236]

- IDA Pro: IDA Pro je freeware demontážník pro hobby použití. A zapojit for V850 is available. Download site is gray for securities.[237]

GUI based debuggers

GUI na základě program debuggery are mainly provided for ladění z sestaven zdrojové kódy. Usually, it is used with simulátory instrukční sady nebo obvodové emulátory.

- Renesas:

- ID850: For the combination of CA850 compiler and SM850 instruction set simulator.

- ID850NW: For the combination of N-Wire based obvodové emulátory.

- ID850QB: For the combination of probing-pod based emulator IEQUBE2

- NDK (Naito Densei Kogyo Co. Ltd, Group): Operation started in 1950 as subsidiary of NEC.

- NW-V850-32

- GHS (Green Hills Software): Multi: General-purpose debugger.

- Red Hat, Inc.: Insight (GDB-Tk): GUI front-end tightly combined with GNU Debugger.

- Mentor Graphics (dříve Accelerated Technology, Inc. ): code|lab Developer Suite[238]

- By N-Wire based in-circuit emulator vendors:

Instruction set simulators

Simulátor instrukční sady, jinými slovy, Virtuální platforma is provided to perform ladění without equipment's Hardware before testing on a real machine.

- Renesas: SM850[241]

- Open Virtual Platform: Simulátor instrukční sady[242]

- Synopsys: VDK for Renesas RH850 MCU[243]

Automated code reviewers

Automated code reviewer, jinými slovy, zdroj code analyzer qualify the level of completeness of written software zdrojový kód. This method is classified as dynamická analýza kódu a statická analýza kódu.

Dynamic code analyzers with simulators

- Renesas: TW850

- TW850 Performance Analysis Tuning Tool is a general utility to improve effectiveness of software.[244]

- Renesas: AZ850

- AZ850 System Performance Analyzer is a utility for RX850 operační systém v reálném čase to evaluate effectiveness of application programs.[245]

- Gaio Technology: Coverage Master winAMS[246]

- Coverage Master winAMS je zdroj pokrytí kódu measurement tool.

Static code analyzers

- GHS (Green Hills Software): DoubleCheck ISA (Integrated Static Analysis) tool[247]

- Rogue Wave Software, Inc: Klocwork[248]

IDE (Integrated Development Environments)

IDE, Integrované vývojové prostředí, is a framework to provide software development functions.

- Renesas: CS+ (dříve CubeSuite+)[249]

- GHS (Green Hills Software): Multi

- Zatmění Pluginy

- Sbírka překladačů GNU (GCC) a GNU Debugger (GDB)

- Pracovní stůl Wind River (formerly Tornado®)

Hardware development tools

ICE (In-circuit emulators)

Většina z obvodové emulátory, such as Rnesas IE850 (dříve IECUBE2),[250]can be used both for V850 Family and for RH850 Family, but may require firmware updating.The latest "trace function" of the JTAG (N-Wire[251]) na základě emulátor v obvodu is replaced from the N-Trace (signalizace s jedním koncem )[252]do Aurora Stopa (diferenciální signalizace ).[253]

Full probing pod type

Full probing pod type emulátor v obvodu is sometimes called as full ICE nebo legacy ICE.

- Renesas IE850 (dříve IECUBE2)[250]

- Naito Densei Machida Mfg. Co., Ltd. (Operation started as NEC's subsidiary.)

- Asmis brand for custom LSIs.[254]

ROM emulator type

- Lauterbach: ROM Monitor for V850[255]:5

- KMC (Kyoto Microcomputer Co., Ltd.): PARTNER-ET II (zastaralé)[256]

JTAG N-Wire and N-Trace type

N-Wire and N-Trace[257][252][258][259]je JTAG -based debugging interface specification, which circuit implementation is called TAP Controller (Test Access Port controller),[260]primarily compiled by Philips N.V. (v současné době NXP Semiconductors ) about a quarter century ago. But it is perhaps not disclosed publicly in its earlier stage. As the result, each semiconductor and emulátor v obvodu vendor implemented similar interfaces independently. Nowadays, it is standardized by IEEE 1149.1 Working Group.[261]

- Renesas

- Naito Densei Machida Mfg. Co., Ltd. (Operation started as NEC's subsidiary.): Asmis značka.[264]

- Midas Lab.: RTE-2000H[265] s PARTNER[127][239] debugger

- Lauterbach: Trace32[255][266][267]

- iSystem: BlueBox iC5000 and iC5700[268][269]

- Systémy IAR

- DTS INSIGHT (formerly YDC; Yokogawa Digital Computer): adviceLUNA II[270][271]

- Computex: PALMiCE3 V850[272]

- Sohwa & Sophia Technologies: Universal Probe Blue[273] s WATCHPOINT debugger[240]

- KMC (Kyoto Microcomputer Co., Ltd.): PARTNER-Jet (zastaralé)[274]

Nexus and Aurora trace type

Nexus nebo IEEE-ISTO 5001-2003 je standard ladění rozhraní pro vestavěné systémy.

Aurora is a high speed signal transfer specification. Své vrstva datového spojení komunikační protokol je point-to-point serial links, a fyzická vrstva je vysoká rychlost diferenciální signalizace.

- Lauterbach: Trace32: PowerTrace for NEXUS[275]

- iSystem: BlueBox iC5000 and iC5700 (Nexus), iC6000 (Aurora)[276][277]

Flash ROM programmers

Because V850 Family is developed as a single chip microcontroller, every product integrates energeticky nezávislá paměť. In its first stage, it was jednorázově programovatelný nebo UV EPROM type, but V853, V850/xxn Series and later, it becomes flash paměť typ.

Gang writers (gang programmers)

A gang writernebo gang programmer, is an old terminologie pro programovatelná ROM writers, or programmers. Its name origin comes from that it steals the binary code from one device, and write it to plural ones simultaneously. Tento read device is sometimes called as a hlavní zařízení. For mass production use, a dedicated attachment board with "a set of sockets," i.e. "a gang," is needed. As usual, instead of a programmed master device, an kód objektu file can be copied from a PC via download cable, or from a USB stick. Většina z gang writers akceptovat ASCII format files such as Intel HEX a Motorola SREC, or binary format files such as ELF.

This method is suitable for mass production.

- TESSERA Technology Inc.: Stick GANG Writer[278]

Programming service providers

Flash ROM programming poskytovatelé služeb exit in most of countries.

- Minato Holdings, Inc.

- Minato Holdings, Inc. (in Japanese)[279] is a Japanese company started as an automatizované zkušební zařízení vendor for memory LSIs. Nowadays, it provides flash ROM programming service for various devices, including V850 and RH850, with its own made gang writers a full automatic device handler stroje.

On board programming with ICE

Většina z JTAG -na základě obvodové emulátory mít na palubě flash ROM programming function via debug port.

May be or may not be IEEE standard 1532-2002; a standard for in-system configuration of programmable components.[280]

Direct connection via RS-232C

If the target board has a RS-232C connector and a transceiver (driver/receiver) IC, such as ICL32xx,[281]pro UARTx peripheral function of V850 device, flash ROM programming with directly connected PC might be available (depends on devices[282]:16–24) Renesas Flash Programmer software V2[283]nebo V3[284]je požadováno.

Dedicated on board programmer

On board programming is also available via UARTx nebo CSIx+HS peripheral on V850 devices by using dedicated programmer hardware (depends on devices[282]:16–24).

- Renesas: PG-FP6[285]

Ancient PROM writers

To program V851[286]:11,14–20and V852,[287]:11,14–20 starověký PROMENÁDA programmer with dedicated adapter is required.

- Renesas PG-1500 (zastaralé)

- Renesas PG-1500[288] je programovatelná ROM writer compatible with 27C1001A[289] zařízení, UV EPROM nebo OTP; one-time PROM. This writer reads silicon signature[290][291] from each device before programming by asserting 12.5 V to A9 (address #9) terminal. It must NOT be used for modern flash ROM hořící.

Gray zone tools

Some gray zone hacking tools exit for V850 on car dashboards.

- VVDI PROG.:

- OBDexpress[292]

Evaluation boards

Viz také

Odkazy a poznámky

- ^ A b C d Harigai, Hisao; Kusuda, Masaori; Kojima, Shingo; Moriyama, Masatoshi; Ienaga, Takashi; Yano, Yoichi (1992-10-22). "低消費電力・低電圧動作の32ビットマイクロプロセッサV810" [A low power consumption and low voltage operation 32-bit RISC Microprocessor] (PDF). SIG Technical Reports, Information Processing Society of Japan. 1992 (82 (1992-ARC-096)): 41–48.

Abstraktní:

An advanced 32-bit RISC microprocessor for embedded control; V810 is introduced in this paper. The V810 has high performance and application specified functions. V810 dissipates less power than any other RISC chips. The V810 is the first 32-bit RISC microprocessor that operates at 2.2 V.

The V810 chip is fabricated by using 0.8 μm CMOS double metal layer process technology to integrate 240,000 transistors on a 7.7×7.7 mm2 zemřít. - ^ "NEC : Shareholder Information". www.nec.com.

- ^ A b NEC (April 1999). "SEMICONDUCTORS SELECTION GUIDE" (PDF) (17. vydání).

- ^ "CA830, CA850 C COMPILER PACKAGES" (PDF). NEC.

- ^ A b C Wang, Bobby (2010-08-04). "V850 Architecture Overview, High performance and Energy Efficient" (PDF). Renesas Electronics Corporation.

- ^ "NEC ND-3530A firmware update like ND-3520A or ND-3540A". Club Myce - Knowledge is Power. 2010-09-04. Citováno 2018-01-29.

- ^ "Optiarc AD7240S". www.cdrinfo.com. Team CDRInfo.COM. 2009-06-29.

Built-in CPU functionality

• Onboard 32-bit RISC CPU (V850ES core)

• Built-in RAM (14KB)

• Power management functionality

• Built-in peripheral circuits (timer, interrupt controller, serial interface) - ^ MOTOYAMA, Yoshiak; SATO, Noboru; HONMA, Hiromi; JIMI, Junich; SHIBATA, Iwao (2006-12-25). "SCOMBO/UM: World's First Optical Drive System LSI to Support Recording/ Playback of Both Next-Generation DVD Formats, HD DVD and BD" (PDF). Nec Technical Journal. NEC. 1 (5): 15–18. ISSN 1880-5884. 200902288400231201.

- ^ "First LSI to Offer Blu-Ray and HD DVD Writing". www.cdrinfo.com. Team CDRInfo.COM. 10. 10. 2006.

- ^ A b C "NEC to Market Ultra-Low Power Consumption, Low-Noise 32-bit RISC Single-Chip Microcontroller Ideal for Portable Equipment". NEC (Tisková zpráva). 1997-08-28.

- ^ "32-BIT RISC MICROCONTROLLER V850/SV1" (PDF). NEC Device Technology International. NEC. 1999 (54).

- ^ V850/SA1 for Hardware (PDF) (4.01 ed.). Renesas. 1. 8. 2005.

- ^ A b "V850/SA1". Renesas Electronics.

- ^ Suto, Shinichi. "32-BIT RISC MICROCONTROLLER V850/SBx" (PDF). NEC Device Technology International. NEC. 1998 (51).

- ^ "NEC 32-bit RISC Single-chip Microcomputer Features High Performance,Ultra-Low Power Consumption, Low Noise and Peripheral Functions". www.nec.co.jp. 1998-08-24.

- ^ "V850/SC1, V850/SC2". Renesas Electronics.

- ^ "NEC Unveils Family of 32-bit RISC Microcontrollers with Optimal Performance/Power Ratios for Consumer, Industrial and Automotive Applications V850/SCx Family MCUs offers large memory options, pin-for-pin compatibility with existing controllers and numerous peripherals". NEC (Tisková zpráva). 2001-04-01.

- ^ Naito, Yukihiro; Hikishima, Naoki; Ohta, Yoshiaki; Hatabu, Atsushi; Kuroda, Ichiro (20 April 2001). "W-CDMA端末用ビデオフォン" [Video-Phone for W-CDMA Terminal] (PDF). The Journal of the Institute of Image Information and Television Engineers (v japonštině). 55 (4): 497–498. doi:10.3169/itej.55.497. ISSN 1881-6908.

- ^ F35-XXL Hardware description (PDF) (1.10 ed.). FALCOM GmbH. 24. 06. 2014.

- ^ Eltze, Jens (1997). "Double-CAN Controller as Bridge for Different CAN Networks" (PDF). 4 Th International CAN Conference. CAN in Automation (CiA) international.

- ^ Ishikawa, Tatsuya. "32-BIT RISC MICROCONTROLLER V850/SF1" (PDF). NEC Device Technology International. NEC. 2000 (57).

- ^ A b Kubota, Kei. "32-BIT RISC SINGLE-CHIP MICROCONTROLLER V850E/MA1" (PDF). NEC Device Technology International. NEC. 1999 (54).

- ^ "V850E/ME2". Renesas Electronics.

- ^ Ohbuchi, E.; Hanaizumi, H.; Lim Ah Hock (2004). "Barcode Readers using the Camera Device in Mobile Phones". 2004 International Conference on Cyberworlds. str. 260–265. CiteSeerX 10.1.1.335.8157. doi:10.1109/CW.2004.23. ISBN 0-7695-2140-1. S2CID 15634963.

- ^ Yun Chan Cho; Jae Wook Jeon (2007). "Current software platforms on mobile phone". 2007 International Conference on Control, Automation and Systems. pp. 1862–1867. doi:10.1109/ICCAS.2007.4406649. S2CID 16120691.

- ^ Kaneko, Yasunori; Fumio, Suto; Umeda, Koji; Shiraishi, Mitsutaka; Shirota, HIrobumi; Suka, Takeya (2002-04-25). "デジタル・ムーバN503iS HYPERの開発" [Development of Digital Mova N503iS HYPER.]. NEC Technical Journal (v japonštině). 55 (4): 156–159. ISSN 0285-4139.

- ^ Kayama, Naoyuki; Mizoguchi, Tamiyuki; Ehara, Tatsuji; Osawa, Takeshi; Umezawa, Atsushi; Yamada, Yasuyoshi (2003-03-10). "ムーバN504iSの開発" [Development of Mova N504iS.]. NEC Technical Journal (v japonštině). 56 (2): 52–55. ISSN 0285-4139.

- ^ Yamashita, Masayoshi; Takenaka, Hidetoshi; Inoue, Jiro; Terada, Shigehiro; Yamada, Hironori; Akiyama, Makoto (2003-09-25). "ムーバN505iの開発" [Development of mova N505i]. NEC Technical Journal (v japonštině). NEC. 56 (8): 33–37. ISSN 0285-4139. 200902227791143957.

- ^ Torihata, Toshiaki. "32-BIT RISC SINGLE-CHIP MICROCONTROLLER V850E/IA1" (PDF). NEC Device Technology International. NEC. 1999 (55).

- ^ Torihata, Toshiaki (2001). "32-BIT RISC SINGLE-CHIP MICROCONTROLLER V850E/IA2" (PDF). NEC Device Technology International. NEC. 2001 (61). S2CID 51805607.

- ^ "NEC Adds Inverter Control Functions in 32-bit Single-chip RISC Microcontroller". NEC (Tisková zpráva). 1999-08-24.

- ^ "V850E/IA3, V850E/IA4". Renesas Electronics.

- ^ Nonaka, Yoshiya; Denda, Akihiro; Uesaka, Gakuji; Sakamoto, Yuji; Nii, Noritaka; Satou, Masahiro; Endo, Kazuaki; Katou, Hiroki; Sugino, Ryouji; Sada, Takeshi; Endo, Koji; Nishigata, Junko; Ishiyama, Kunihiro; Morita, Kenji (2002). "HDD-DEH のソフトウェア開発" [Software Development of CD/MP3/Memory Stick Player with HDD] (PDF). Pioneer R&D (v japonštině). Pioneer Corporation. 12 (3): 26–38.

Souhrn:

We developed this product which carries new functions, CD( includes MP3CD playback), MagicGate Memory Stick (recording & playback & updating) and HDD (recording & playback), for the first time as a car audio product. This product for the worldwide market is packed into 1DIN size, with standard features (AM/FM Tuner, MOS-FET50Wx4ch amplifier, OrganicEL display, and sound field control DSP) and the new functions. We considered the operation carefully to handle many music files in the HDD easily. We concentrated on making a new field of audio entertainment, and we were the first to introduce this system on the car audio market. - ^ "V850ES/SA2, V850ES/SA3". Renesas Electronics.

- ^ Kochkov, A. (October 2014). "Reversing firmware using radare2 [H2HC]" (PDF).

- ^ V850 Series Development Environment Pamphlet (PDF) (5.00 ed.). Renesas. 2006-02-01.

- ^ "V850E2/Px4". Renesas Electronics.

- ^ Matsuyama, Hideki (April 18, 2003). "V850E2: The High Performance CPU Platform which realize Various Application Systems with Flexible Memory Configurations". www.coolchips.org. COOL Chips VI.

- ^ A b "V850 Family". Renesas Electronics.

- ^ "RH850 Family (Automotive only)". Renesas Electronics.

- ^ A b "Trademark Notice". www.renesas.com. Renesas.

- ^ "Trademark application T2001-067573". 2001-07-25.

Result: application refused

- ^ "V850 Embedded Microcontroller". www.tmdn.org. 2004-12-18.

Result: application refused

- ^ Schmerling, Holger (2006). "AUTOSAR FlexRay driver now available for microcontrollers" (PDF). System@IC News. NEC Electronics. 2006 (4): 3. S2CID 15509410.

- ^ V850E/PH2: Hardware (PDF) (1.00 ed.). NEC Electronics. Ledna 2007. str. 33.

- ^ Quick time-to-market with Renesas Synergy Platform and Cool Phoenix 3 (PDF) (1.00 ed.). Renesas. Říjen 2016.

- ^ "TMVIEW: PHOENIX 3". www.tmdn.org.

- ^ A b C d E F V850 FAMILY 32-bit Single-Chip Microcontroller Architecture (PDF) (7. vydání). Renesas Electronics. Březen 2001.

- ^ "RH何某というのはSHのコアなのですか?" [Does RH-something employ SH core?]. Renesas Rulz - Japan. Renesas Electronics. 2017-03-29.

- ^ "Could anyone please tells me the major differences between the RH850 and V850 families ? | GNU Tools". gcc-renesas.com.

- ^ A b C d E F G h i "V810 Seminar" (PDF). NEC Corporation. 1995-02-21.

- ^ A b C d V810 FAMILYTM 32-BIT MICROPROCESSOR ARCHITECTURE (PDF) (1. vyd.). NEC Corporation. Říjen 1995.

- ^ Engblom, Jakob (2003). "Embedded Systems Computer Architecture" (PDF). Extended Abstract from ESSES 2003. S2CID 15760973.

Code size is an important factor in most embedded designs, and instruction sets are designed and extended with code size in mind. Fairly typically, the NEC V850 architecture uses 16-, 32-, 48-bit, and 64-bit instructions to encode a RISC-style instruction set. The 32-bit ARM and MIPS architecture have been extended with reduced 16-bit instruction sets in order to reduce the code size. Instructions that perform a lot of work, like loading multiple values from the stack, are popular to reduce code size. - ^ "GCC: V850 Options". gcc.gnu.org. Free Software Foundation, Inc.

- ^ Kaneko, Hiroaki; Sakurai, Yoshikazu; Nasu, Masaki; Katsuta, Hiroshi; Nagasaki, Kazunori; Hiiragizawa, Yasunori; Sonobe, Satoru; Onishi, Tatsuro; Tokunaga, Kei (March 1995). "高性能・低消費電力動作の32ビットRISCシングルチップマイクロコンピュータV851" [High Performance and Low-Power-Consumption 32-bit RISC Single Chip Microcomputer V851.]. NEC Technical Journal. Special Issue on Semiconductor Devices. (v japonštině). NEC Corporation. 48 (3): 42–48. ISSN 0285-4139.

- ^ Yamagata, Yasushi; Ishibashi, Takashi; Sano, Yuichi; Koga, Yoshikazu; Yoshida, Miho; Sugo, Akihisa (April 1996). "32ビットRISCマイクロコントローラV853" [32-bit RISC Microcontroller V853.]. NEC Technical Journal. Special Issue: Semiconductor Devices. (v japonštině). NEC Corporation. 49 (3): 55–60. ISSN 0285-4139.

- ^ A b Krämer, Michael (2011-01-21). "Latest 32-bit RISC architecture for automotive expands functionality". EE Times.

All V850 products are upwards compatible. As a result, today's sophisticated components can still execute the same instructions as their forebears. The architecture has undergone continual improvements with extensions to the instruction set, and today it offers computing power of up to 2.6 Dhrystone MIPS/MHz. Further performance increases can be achieved by integrating several of these processor cores on a single chip, delivering twice or even four times more computing power. - ^ A b "First 32-bit RISC Microcontroller with Integrated Flash Memory Offered by NEC Electronics Newest Product in Company's V800 Series Operates at 33 MHz. - Free Online Library". www.thefreelibrary.com. OBCHODNÍ DRÁT. 1996-03-04.

- ^ UPD70F3003A,70F3025A,70F3003A(A) Data Sheet (PDF) (5.01 ed.). Renesas. 1. 8. 2005. str. 37.

- ^ Matsumoto, Yoichi (1999). "NEXT STEP: NEC'S STRATEGY FOR RISC MICROCOMPUTERS" (PDF). NEC Device Technology International. NEC. 1999 (5).

- ^ V850E1 for Architecture (PDF) (3.01 ed.). Renesas. 01.02.2004.

- ^ A b "NEC Launches 32-Bit RISC Single-chip Microcontroller for Ultra-low-power Mobile Applications". www.nec.co.jp. NEC: Press Release. 2001-08-23.

- ^ "NEC Releases Java Accelerator for 32-Bit RISC V850 Microcontrollers". www.nec.co.jp. NEC. 2001-11-15.

- ^ Aoki, Yayoi (2001-11-30). "US 6,948,034 B2; Method for use of stack" (PDF). pdfpiw.uspto.gov.

The present invention relates to a method for use of a stack in a Java accelerator device.

- ^ Mine, Kazumasa (2000-11-21). "US 7,200,741 B1: Microprocessor having main processor and co-processor" (PDF). pdfpiw.uspto.gov. Úřad pro patenty a ochranné známky Spojených států.

With such arrangement, the microprocessor can flexibly deal with various kinds of instruction sets with different architectures such as an instruction set for an interpreter language for realizing a virtual machine for Java and an instruction set for emulating another microprocessor.

- ^ "NEC Electronics Introduces 32-Bit V850E2/ME3 Microcontroller for High-Performance, Real-Time Processing; Most Advanced V850 Microcontroller Enables Performance of 400MIPS at 200MHz. - Free Online Library". www.thefreelibrary.com. 2005.

- ^ A b "NEC Electronics Introduces Next-Generation V850E2M Dual-Core Architecture For 32-Bit V850 Microcontrollers". www.businesswire.com. Obchodní drát. 2009-04-20.

- ^ Whytock, Paul (2010-10-14). "Next-Gen 32Bit V850 CPU Core Features SIMD Support". Elektronický design.

- ^ Kumura, Takahiro; Taga, Soichiro; Ishiura, Nagisa; Takeuchi, Yoshinori; Imai, Masaharu (2010-08-16). "Software Development Tool Generation Method Suitable for Instruction Set Extension of Embedded Processors" (PDF). IPSJ Transactions on System LSI Design Methodology. Information Processing Society of Japan. 3: 207–221. doi:10.2197/ipsjtsldm.3.207. ISSN 1882-6687.

- ^ "No matches were found for your search term(s)". Renesas.

- ^ Harigai, Hisao; Kusuda, Masahiro; Kojima, Shingo; Moriyama, Masatoshi; Ienaga, Takashi; Yano, Yoichi (1992-10-22). "A low power consumption and low voltage operation 32-bit RISC Microprocessor" (PDF). SIG ARC Technical Reports (v japonštině). Information Processing Society of Japan. 1992 (82 (1992-ARC-096)): 41–48. AN10096105.

Abstraktní:

An advanced 32-bit RISC microprocessor for embedded control; V810 is introduced in this paper. V810 má vysoký výkon a funkce specifikované aplikací.

V810 rozptyluje méně energie než jakékoli jiné čipy RISC. V810 je první 32bitový mikroprocesor RISC, který pracuje při 2,2 V.

Čip V810 je vyroben pomocí technologie zpracování dvojité kovové vrstvy CMOS 0,8 μm k integraci 240 000 tranzistorů na 7,7 × 7,7 mm2 zemřít. - ^ Kusuda, Masahiro; Hirai, Miho; Suzuki, Hiroaki; Daito, Masayuki; Suzuki, Chika; Kimura, Akiko; Demura, Shigeki; Ishibashi, Takashi; Sato, Syoichiro (září 1992). „低 消費 電力 ・ 低 電 圧 動作 の オ リ ジ ナ ル 32 ビ ッ ト RISC マ イ ク ロ プ ロ セ ッ サ V810“ [V810 - nízká spotřeba energie a nízkonapěťový provoz 32bitový mikroprocesor RISC.] (obrázek / jp2). Technický věstník NEC (v japonštině). NEC Corporation. 45 (8): 66–73. ISSN 0285-4139. 000000018731.

- ^ A b C d E Kuwata, Takaaki. „ロ ジ ッ ク プ ロ セ ス シ リ コ ン ロ ジ ッ ク プ ロ セ ス ロ ジ ッ ク プ ロ セ ス の 開 発 も の が た り“ [Vývojový příběh procesu křemíkové logiky] (PDF) (v japonštině). Muzeum historie polovodičů v Japonsku. Citovat deník vyžaduje

| deník =(Pomoc) - ^ V850 / SA1 pro hardware (PDF) (4.01 ed.). Renesas. 1. 8. 2005.

- ^ OCHI, MASATOSHI; ISHIKAWA, HIROTAKA; TSUJI, NOBUHIRO; TAKEDA, MITSURU; SUTO, SHIN'ICHI; ISHIKAWA, TATSUYA (2001-03-23). „32 ビ ッ ト RISC マ イ ク ロ コ ン ト ロ ー ラ V850 / SBX の EMI ノ イ ズ 低 減“ [EMI Noise Reduction of 32bit RISC Microcontroller V850 / SBX.]. Technický věstník NEC (v japonštině). NEC. 54 (3): 41–44. ISSN 0285-4139.

- ^ 32bitový jednočipový hardware mikrokontrolérů V850ES / SA2, V850ES / SA3 (PDF) (2,01 ed.). Reneas. Srpna 2005.

- ^ A b V850ES / JG3-L Uživatelská příručka: Hardware (PDF) (9,00 ed.). Renesas. 2014-03-14.

- ^ A b „NEC oznamuje novou procesní technologii pro nejpokročilejší systém LSI na světě - první 0,13 mikronová procesní technologie na světě -“. www.nec.co.jp. 1999-10-04.

- ^ „RH850 & RL78 - nová generace automobilových mikrokontrolérů -“. slideplayer.com.

- ^ „PC-FXGA - WIP“. Super CD · Rom² à GoGo. 2015-12-13.

- ^ 32bitová mikroprocesorová architektura V810 FAMILY (PDF) (1. vyd.). NEC Corporation. Říjen 1995.

- ^ A b C „Novější překladač GCC.« Virtual Boy Development Board «Fórum« Planet Virtual Boy ”. www.planetvb.com.

- ^ Suzuki, Hiroaki; Suzuki, Chika; Kimura, Akiko; Sato, Syoichiro; Ide, Syuichi; Sakanaka, Yasuhide (1993-01-22). „32bitový mikroprocesor RISC V810 a jeho návrhové techniky“ (PDF). Technické zprávy SIG SLDM. 1992-SLDM-065 (v japonštině). Information Processing Society of Japan. 1993 (6): 155–162. AA11451459.

Abstraktní:

Pokročilý 32bitový mikroprocesor RISC pro vestavěné ovládací prvky; V810 a jeho návrhová technika jsou popsány v tomto článku. Model V810 je vyroben pomocí technologie zpracování dvojité kovové vrstvy 0,8 μm CMOS k integraci 240 000 transisterů na 7,7 × 7,7 mm2 zemřít. Při návrhu modelu V810 jsme použili techniky automatizace návrhu. Před výrobou byla u modelu V810 analyzována logická správnost a časové omezení. Nakonec V810 nejprve správně provedl benchmarky realtime OS a SPEC. - ^ Akaboshi, Hiroki; Yasuura, Hiroto (08.03.1995). „Porovnání designu jazyků popisu hardwaru na úrovni RT“ (PDF). Poznámky IPSJ SIG (v japonštině). Information Processing Society of Japan. 1995 (24 (1994-SLDM-074)): 57–64.

Abstraktní:

Pokrok v syntéze logiky / rozvržení umožňuje navrhovat obvody pomocí hardwarových popisových jazyků (HDL). Když je navržený obvod malý, syntetizuje se automaticky z popisu HDL. V tomto článku, abychom objasnili, jaké druhy problémů existují při navrhování velkého obvodu, který vypadá jako procesor, navrhneme procesor a některé jeho součásti pomocí HDL na úrovni RT a vyhodnotíme obvody syntetizované nástrojem pro logickou / rozložení syntézy. - ^ Tamura, K. A. (1989). "Vyhledání funkčních chyb v logických obvodech" (PDF). Sborník příspěvků z 26. konference ACM / IEEE o konferenci Design Automation Conference - DAC '89. 185–191. doi:10.1145/74382.74414. ISBN 0897913108. S2CID 2364060.

- ^ Kato, S .; Sasaki, T. (září 1983). FDL: Jazyk popisu strukturálního chování. 6. mezinárodní symposium o popisu hardwaru počítačů Jazyk a jejich aplikace. Elsevier Science Ltd. str. 137–152. ISBN 978-0444866332.

- ^ Yano, Yoichi (duben 2012). „32 ビ ッ ト ・ マ イ コ ン「 V60 」開 発 物語“ [Vývojový příběh modelu V60; 32bitový mikroprocesor] (PDF). Encor (v japonštině). Společnost specialistů na průmysl polovodičů (75): 17–20.

- ^ Sutherland, Stuart (2013). Příručka Verilog PLI: Uživatelská příručka a podrobný odkaz na rozhraní programovacího jazyka Verilog. Springer Science & Business Media. str. 3. ISBN 9781461550174.

- ^ Inasaka, červen; Ikeda, Rikikazu; Umezawa, Kazuhiko; Yoshikawa, Ko; Yamada, Shitaka; Kitawaki, Shigemune (leden 2003). „Hardwarová technologie simulátoru Země“ (PDF). Výzkum a vývoj NEC. Architektura a hardware pro HPC. 44 (1): 27–36.

- ^ „Ochranné známky“. www.mentor.com. Mentor Graphics.

- ^ „Mentor Graphics and Pyxis Technology“. www.mentor.com. Mentor Graphics.

- ^ „Návody k návrhu nanometrů IC - Santa Clara University“. www.mentor.com. Univerzita Santa Clara.

- ^ Jansen, Dirk (2010-02-23). Příručka pro automatizaci elektronického designu. Springer Science & Business Media. str. 54. ISBN 9780387735436.

Design Architect od společnosti Mentor Graphics Corporation s programy NETED a SYMED. Tento systém je nejuniverzálnější ze tří [3.3].

Je použita verze C1 na HP Unix V10.20 (zkrácená forma MENTOR) - ^ „CB-C8 3-VOLT, 0,5-MIKRONOVÝ BUNĚČNÝ CMOS ASIC“ (PDF). NEC. Červenec 1994: 7. Citovat deník vyžaduje

| deník =(Pomoc) - ^ Harlow III, Justin E. (1986). Co by měl každý inženýr vědět o inženýrských stanicích. CRC Press. str. 47. ISBN 9780824775094.

- ^ Kang, Sungho. „Ověření I“ (PDF). Kurzový materiál univerzity Yonsei.

- ^ Takasaki, S .; Sasaki, T .; Nomizu, N .; Ishikura, H .; Koike, N. (1986). „HAL II: Mixed Level Hardware Logic Simulation System“ (PDF). 23. konference ACM / IEEE Design Automation Conference. 581–587. doi:10.1109 / DAC.1986.1586146. ISBN 0-8186-0702-5.

- ^ „Používání GNU Compiler Collection (GCC): Možnosti V850“. gcc.gnu.org.

- ^ A b „民生 用 マ ル チ メ デ ィ ア 機器 向 け 32 ビ ッ ト オ リ ジ ナ ル RISC 型 マ イ ク ロ プ ロ セ ッ サ の 発 売 に つ い て ~ ロ ッ ッ た た た た た た た た た た た た た た た た. www.nec.co.jp (v japonštině). 1995-03-22. Citováno 5. února 2018.

- ^ "Souhrn architektury V810" (PDF). www.planetvb.com. Planet Virtual Boy.

Ze semináře V810.

- ^ A b C Suzuki, Hiroaki; Sakai, Toshichika; Harigai, Hisao; Yano, Yoichi (1995-04-25). „32bitový mikroprocesor CMOS 0,9 V, 2,5 MHz“. IEICE TRANSACTIONS on Electronics. E78-C (4): 389–393. ISSN 0916-8516. Citováno 2018-01-09.

Souhrn:

32bitový mikroprocesor RISC „V810“, který má pětistupňovou strukturu potrubí a 1kbajtovou mezipaměť instrukcí s přímým mapováním, realizuje provoz 2,5 MHz při 0,9 V se spotřebou energie 2,0 mW. Napájecí napětí lze snížit na 0,75 V. K překonání úzké meze šumu jsou všechny signály nastaveny tak, aby měly střídání mezi kolejnicemi technikou pseudo-statického obvodu. Čip je vyroben procesní technologií CMOS s dvojitou kovovou vrstvou 0,8 μm pro integraci 240 000 tranzistorů na matrici 7,4 × 7,1 mm. - ^ A b Nakayama, Naoko; Tsukamoto, Hirokazu. „VYSOKÝ VÝKON 32bitový RISCOVÝ MIKROPROCESOR V832“ (PDF). NEC Device Technology International. NEC. 1998 (51).

- ^ A b „Produktový list řady V850 - V851“ (PDF). datasheetarchive.com. NEC.

- ^ A b „Produktový list řady V850 - V853“ (PDF). datasheetarchive.com. NEC.

- ^ A b „世界 で 初 め て フ ラ ッ シ ュ メ モ リ を 内 蔵 し た 32 ビ ッ ト RISC 型 マ イ ク コ コ ン ロ ー ラ の 発 売 に つ い て“. www.nec.co.jp. 1996-03-12. Citováno 2018-02-01.

- ^ A b „Společnost NEC uvádí 32bitové jednočipové mikroprocesory RISC, které obsahují 3,3 V flash paměť a pracují na 40 MHz“. www.nec.co.jp. 1997-04-08.

- ^ A b „Hlavní specifikace jádra procesoru V850E“. www.nec.co.jp. 1997-04-08.

- ^ A b C d E Kimura, Akira (jaro 2000). "CPU CORE PRO SYSTÉM LSI V850E / VR4120A " (PDF). NEC Device Technology International. 2000 (57).

- ^ A b „SPECIFIKACE KIT-NB85E-TP (-H)“. Midas Lab Inc.

- ^ A b C d „SPECIFIKACE KIT-NA85E2-TP (-H)“. www.midas.co.jp. Midas Lab Inc.

- ^ A b C d E F SAKURAI, Yoshikazu; SUZUK, Hiroaki; MAEMURA, Kouji; TAKAKURA, Satoshi (prosinec 2006). „Současný stav vestavěného CPU v designu SoC“ (PDF). NEC Technické. 1 (5): 38–41.

- ^ A b „Renesas Electronics ohlašuje vývoj 32bitového jádra procesoru V850 ™ nové generace s podporou SIMD, která poskytuje vylepšené zpracování signálu“. Renesas Electronics. 2010-10-01.

- ^ A b C d E Design Manual: CB-9 Family VX / VM Type Core Library (PDF) (5. vydání). NEC.

- ^ A b Sugimoto, Hideki; Sakairi, Tetsuya; Matoba, Shoichiro; Akaike, Yukihiki; Matsuyama, Hideki (březen 1998). „32 ビ ッ ト RISC CPU V850E 搭載 コ ア「 NA85E 」“ [32bitové jádro RISC CPU "NA85E".]. Technický věstník NEC. Zvláštní vydání: Polovodičová zařízení. Polovodičová zařízení pro počítačové systémy. Mikropočítače. (v japonštině). 51 (3): 36–39. ISSN 0285-4139.

- ^ A b Sugimoto, Hideki; Ikeuchi, Tooru (2000-03-30). „32 ビ ツ ト RISC CPU V850E 搭載 コ ア「 NB85E 」32bitové RISC CPU jádro“ NB85E"" [32bitové jádro RISC CPU "NB85E".]. Technický věstník NEC. Zvláštní vydání: Polovodičová zařízení; Základní technologie (v japonštině). NEC. 53 (4): 159–162. ISSN 0285-4139. 200902106221942927.

- ^ Sugimoto, Hideki (23. 3. 2001). „RISC プ ロ セ ッ サ Nx85E2 CPU“ [Procesor RISC Nx85E2.]. Technický věstník NEC (v japonštině). NEC. 54 (3): 30–33. ISSN 0285-4139.

- ^ „dNTSC“. Svobodný slovník.

- ^ Simovič, Slobodan; Radivojevič, Ivan P .; Endres, T. J .; Bentson, Tom; Bingham, Ray; Blair, Tony; Cowling, Tom; Eylander, Mark; Fagan, Rory; Long, Chris; Longino, Jim; Olson, Dan; Subia, Rollen; Whitcomb, Doug (2003). „ReX: Přijímač dNTSC systém na čipu“ (PDF). Prezentace HotChips15. HotChips. 15: 9–10.

- ^ NEC Electronics (červenec 2004). 32bitová mikroprocesorová architektura V850E2 (PDF) (Předběžné vydání.). str. 230–233.

- ^ „Omezení použití 32bitových mikrokontrolérů V850 / ME3“ (PDF). 2006-11-02.

- ^ A b „NEC porušuje bariéru o velikosti 0,10 mikronu pomocí rodiny IC na bázi buněk CB-130 a procesní technologie UX5“. www.nec.co.jp. 2000-10-30.

- ^ A b "Základní sestava a seznam specifikací pro CB-130". www.nec.co.jp. 2000-10-30.

- ^ A b „NEC licence V850E mikroprocesorové jádro pro Synopsys - dohoda poskytuje 25 000 návrhářů registrovaných v Synopsys přístup k jádru CPU pro vývoj SoC -“. nec.co.jp. NEC Corporation. 2010-10-01.

- ^ A b „Synopsys DesignWare IP umožňuje Full-Service SoC Design Foundry pro globální UniChip“. Synopsys.

- ^ „Jádro mikrokontroléru RISC s 32 bity V851“ (PDF). 4donline.ihs.com. NEC. 1998.

- ^ „Jádro mikrokontroléru V853 32-bit“ (PDF). 4donline.ihs.com. NEC. 1997.

- ^ A b C d E F G h i PARTNER Uživatelská příručka Řada V800 „NB85E-TP Part Edition“ (PDF) (2.13 ed.). Midas Lab. Inc. 2003-12-10.

- ^ A b C d E F G h Uživatelská příručka KIT-NB85E-TP (PDF) (3.14 ed.). Midas Lab. Co., Ltd. 2003-05-12.

- ^ A b C d E F G h i j Kimura, Akira (2000). „CPU CORE PRO SYSTÉM LSI V850E / VR4120A“ (PDF). NEC Device Technology International. NEC. 2000 (57).

- ^ A b C d 32bitový mikroprocesorový hardware NU85E: NU85E, NU85EA (PDF) (3. vyd.). NEC. Březen 2002.

- ^ A b C Řadič paměti NT85E500, NDT85E500V10, NT85E502 (PDF) (3. vyd.). NEC. Září 2002.

- ^ A b C d E Paměťový řadič NA85E535, NBA85E535Vxx (PDF) (2. vyd.). NEC. Říjen 2002.

- ^ A b KIT-NA85E2-TP (-H) ユ ー ザ ー ズ ・ マ ニ ュ ア ル (PDF) (v japonštině). Midas Lab. Co., Ltd. 05.01.2006. str. 1,00.

- ^ „NEC zužuje délku brány pod 0,10 mikronu | EE Times“. EETimes. 2000-10-31.

NEC také poskytne interně vyvinuté procesory V850E a VRx, ačkoli Mabuchi uvedl, že věří, že NEC bude muset licencovat jádro ARM9, aby oslovil trh mobilních terminálů. - ^ Matsui, Kenji. „RISCOVÁ MIKROPOČÍTAČOVÁ REFERENČNÍ PLATFORMA“ (PDF). NEC Device Technology International. NEC. 2000 (58).

- ^ „Společnost NEC Electronics dosáhla klíčového milníku v iniciativě ACE-2; zkracuje dobu obratu na úrovni systému o více než 30 procent

Společnost také odhaluje druhou fázi své metodiky návrhu otevřeného systému ". www.nec.co.jp. NEC: Tisková zpráva. 2000-05-15. - ^ Nishiguchi, Nobuyuki (02.02.2001). „シ ス テ ム LSI の 未来 は 、 NEC が 拓 く - 設計 環境 の 現状 と 今後 -“ [Návrhová prostředí systému LSI, dnes a budoucnost] (PDF) (v japonštině). NEC Corporation.

- ^ YAMADA, Kazuo; NISHIMOTO, Hiroaki; DAITO, Masayuki; ONO, Hirohiko (prosinec 2007). „Ověření návrhu procesoru pomocí hybridního emulátoru“ (PDF). Technický věstník NEC. 2 (4): 51–55.

- ^ „PFESiP® EP-1 Evaluation Board“. datasheetarchive.com (v japonštině). Renesas. Srpna 2008.

- ^ Vyhodnocovací deska PFESiP® EP-1 Lite 技術 情報 編 (PDF) (v japonštině) (1. vyd.). Renesas Electronics. Září 2008.

A19354JJ1V1UM00

- ^ „PFESiP® (Platforma pro vestavěný systém v balíčku) EP Series EP-3“ (PDF) (v japonštině). Renesas. Květen 2010.

Jádro procesoru V850E2M , max. 266 MHz provoz

- ^ „Companion Chip Reference FPGA Designs“. www.logicbricks.com.

- ^ „Vývojové kity Xylon logiCRAFT-CC zrychlují vývoj doprovodných čipů FPGA pro populární vestavěné procesory“. www.chipestimate.com.

- ^ „Společnost Renesas Electronics představuje řadu mikrokontrolérů V850 4. generace se 74 samostatnými zařízeními pro karoserie automobilů, palubní desky, podvozky a bezpečnostní aplikace“ (Tisková zpráva). Renesas. 4. 11. 2010.

- ^ „Renesas - nové MCU pro automobilové karoserie, palubní desky, podvozky a bezpečnostní aplikace“. www.electropages.com.

- ^ „V850ES / Fx3“. Renesas Electronics. Citováno 2018-01-28.

- ^ „Product Longevity Program (PLP)“. Renesas Electronics.

- ^ „32bitové mikroprocesory řady V850E2 / Jx4 s extrémně nízkou spotřebou - migrace z mikroprocesorů V850ES / Jx3 -“ (PDF). Renesas.

- ^ „32bitové MCU s ultra nízkou spotřebou řady V850 / Jx4“ (PDF). Renesas. Březen 2012.

- ^ Yano, Y .; Koumoto, Y .; Sato, Y. (1988). „Mikroprocesor V60 / V70 a jeho systémy podporují funkce“. Přehled dokumentů. COMPCON jaro 88 Třicátá třetí mezinárodní konference IEEE Computer Society. str.36–42. doi:10.1109 / CMPCON.1988.4824. ISBN 0-8186-0828-5. S2CID 9186701.

- ^ Mizuhashi, Yukiko; Teramoto, Msanoro (srpen 1989). "Operační systém UNIX v reálném čase: RX-UX 832". Mikroprocesorování a mikroprogramování. 27 (1–5): 533–538. doi:10.1016/0165-6074(89)90105-1.

Abstraktní:

Tento článek popisuje požadavky na operační systémy UNIX v reálném čase, koncepci návrhu a implementaci operačního systému UNIX v reálném čase RX-UX 832 pro mikroprocesory v60 / v70, které jsou 32bitovými mikroprocesory NEC. RX-UX 832 je implementován s využitím struktury stavebních bloků, která se skládá ze tří modulů, jádra v reálném čase, souborového serveru a správce Unixu. Aby byla zaručena odpovědnost v reálném čase, bylo zavedeno několik vylepšení, jako je schéma plánování úloh s pevnou prioritou, souvislý systém souborů bloků a funkce odolné vůči chybám.