Složité programovatelné logické zařízení - Complex programmable logic device

tento článek potřebuje další citace pro ověření. (listopad 2013) (Zjistěte, jak a kdy odstranit tuto zprávu šablony) |

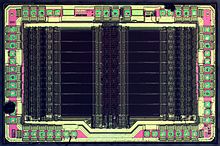

A komplexní programovatelné logické zařízení (CPLD) je programovatelné logické zařízení se složitostí mezi PAL a FPGA a architektonické prvky obou. Hlavním stavebním kamenem CPLD je a makrobuňka, který obsahuje implementaci logiky disjunktivní normální forma výrazy a specializovanější logické operace.

Funkce

Některé funkce CPLD jsou společné s PAL:

- Energeticky nezávislá konfigurační paměť. Na rozdíl od mnoha FPGA, externí konfigurace ROM není vyžadováno a CPLD může fungovat okamžitě po spuštění systému.

- U mnoha starších zařízení CPLD omezuje směrování většinu logických bloků tak, aby měly vstupní a výstupní signály připojené k externím kolíkům, což snižuje příležitosti pro interní ukládání stavu a hluboce vrstvenou logiku. To obvykle není faktorem pro větší CPLD a novější rodiny produktů CPLD.

Další funkce jsou společné s FPGA:

- K dispozici velké množství bran. CPLD mají obvykle ekvivalent tisíců až desítek tisíc logické brány, což umožňuje implementaci středně komplikovaných zařízení pro zpracování dat. PAL mají obvykle maximálně několik stovek hradlových ekvivalentů, zatímco FPGA se obvykle pohybují od desítek tisíc do několika milionů.

- Některá ustanovení pro logiku pružnější než součet produktu výrazy, včetně komplikovaných cest zpětné vazby mezi buňkami makra, a specializovaná logika pro implementaci různých běžně používaných funkcí, jako např celé číslo aritmetický.

Nejviditelnějším rozdílem mezi velkou CPLD a malou FPGA je přítomnost energeticky nezávislé paměti na čipu v CPLD, což umožňuje použití CPLD pro „zavaděč "funkce před předáním řízení jiným zařízením, která nemají vlastní trvalé programové úložiště. Dobrým příkladem je situace, kdy se CPLD používá k načtení konfiguračních dat pro FPGA z energeticky nezávislé paměti."[1]

Rozdíly

CPLD byly evolučním krokem od ještě menších zařízení, která jim předcházela, PLA (poprvé odesláno Signetics ), a PAL. Ty zase předcházely standardní logika produkty, které nenabízely žádnou programovatelnost a byly použity k vytvoření logických funkcí fyzickým zapojením několika standardních logických čipů (nebo stovek z nich) dohromady (obvykle pomocí zapojení na desce nebo deskách s plošnými spoji, ale někdy, zejména pro prototypování drátěný obal elektrické vedení).

Hlavní rozdíl mezi architekturami zařízení FPGA a CPLD je ten, že FPGA jsou interně založeny na vyhledávací tabulky (LUT), zatímco CPLD tvoří logické funkce s mořské brány (například součet produktů).

Viz také

- Jazyk:

- Výrobci:

- Altera (Nyní Intel)

- Atmel (Nyní mikročip)

- Cypress Semiconductor

- Lattice Semiconductor

- Xilinx

- Technologie:

- Integrovaný obvod specifický pro aplikaci (ASIC)

- Smazatelné programovatelné logické zařízení (EPLD)

- Jednoduché programovatelné logické zařízení (SPLD)

- Pole makrobuněk

- Logika programovatelného pole (KAMARÁD)

- Programovatelné logické pole (PLA)

- Programovatelné logické zařízení (PLD)

- Obecná logika pole (GAL)

- Programovatelná elektricky mazatelná logika (KŮRA)

- Polní programovatelné hradlové pole (FPGA)

externí odkazy

Reference

- ^ "Složité programovatelné logické zařízení". blogspot.com. Květen 2008. Citováno 2013-11-17.