Zmije (elektronika) - Adder (electronics)

| Část série na | |||||||

| aritmetické logické obvody | |||||||

|---|---|---|---|---|---|---|---|

| Rychlá navigace | |||||||

Součásti

| |||||||

Kategorie

| |||||||

Viz také | |||||||

An zmije je digitální obvod který vystupuje přidání čísel. v mnoha počítače a další druhy procesory v aritmetické logické jednotky nebo ALU. Používají se také v jiných částech procesoru, kde se používají k výpočtu adresy, tabulkové indexy, operátory přírůstku a úbytku a podobné operace.

Ačkoli pro mnoho mohou být konstruovány doplňky počet reprezentací, jako binárně kódované desetinné místo nebo přebytek-3, fungují nejběžnější doplňky binární čísla V případech, kdy doplněk dvou nebo doplněk se používá k reprezentaci záporná čísla, je triviální upravit zmije na sčítač – odečítač.Jiný podepsané číselné reprezentace vyžadují více logiky kolem základní zmije.

Binární sčítače

Napůl zmije

The napůl zmije přidá dvě jednoduché binární číslice A a B. Má dva výstupy, součet (S) a nosit (C). Signál přenosu představuje přetékat do další číslice víceciferného sčítání. Hodnota součtu je 2C + S. Nejjednodušší design polovičního zmije, zobrazený vpravo, obsahuje znak XOR brána pro S a A brána pro C. Logická logika pro součet (v tomto případě S) bude A'B + AB ' zatímco pro nošení (C) bude AB. S přidáním NEBO brána kombinovat jejich výstupy přenášení lze kombinovat dva poloviční sčítače, aby se celá sčítačka.[1] Poloviční sčítač přidává dva vstupní bity a generuje přenos a součet, což jsou dva výstupy polovičního sčítače. Vstup proměnné poloviny zmije se nazývají augend a addend bity. Výstupní proměnné jsou součet a carry. The pravdivostní tabulka pro poloviční zmije je:

Vstupy Výstupy A B C S 0 0 0 0 1 0 0 1 0 1 0 1 1 1 1 0

Plná zmije

A plný zmije přidává binární čísla a účty pro hodnoty přenášené dovnitř i ven. Jednobitový sčítač přidává tři jednobitová čísla, často psaná jako A, B, a Cv; A a B jsou operandy a Cv je trochu přenesen z předchozí méně významné etapy.[2] Celá sčítačka je obvykle součástí kaskády sčítačů, které přidávají 8, 16, 32 atd. Bitová binární čísla. Obvod produkuje dvoubitový výstup. Výstupní přenos a součet typicky reprezentovaný signály Cven a S, kde se součet rovná 2Cven + S.

Plnou sčítačku lze implementovat mnoha různými způsoby, například pomocí vlastního tranzistor -úrovňový okruh nebo složený z jiných bran. Jeden příklad implementace je s S = A ⊕ B ⊕ Cv a Cven = (A ⋅ B) + (Cv ⋅ (A ⊕ B)).

V této implementaci konečná NEBO brána před tím, než může být výstupní výstup nahrazen XOR brána beze změny výsledné logiky. Použití pouze dvou typů bran je vhodné, pokud je obvod implementován pomocí jednoduchého integrovaný obvod čipy, které obsahují pouze jeden typ brány na čip.

Plnou sčítačku lze také sestrojit ze dvou polovičních doplňků připojením A a B na vstup jedné poloviční sčítačky, poté vezmeme její souhrnný výstup S jako jeden ze vstupů do druhé poloviny zmije a Cv jako jeho další vstup a nakonec jsou nosné výstupy ze dvou polovičních sčítačů připojeny k bráně OR. Součet výstupu z druhé poloviny zmije je výsledný součet (S) plného sčítače a výstup z brány OR je konečným výstupem přenosu (Cven). Kritická cesta úplného sčítače prochází oběma branami XOR a končí součtem bitů s. Za předpokladu, že XOR brána trvá 1 zpoždění, je zpoždění uložené kritickou cestou úplné sčítačky rovné

Kritická cesta přenášení prochází jednou bránou XOR v sčítači a 2 branami (AND a OR) v bloku přenášení, a proto, pokud brána AND nebo OR trvá 1 zpoždění, má zpoždění

The pravdivostní tabulka pro celou zmije je:

Vstupy Výstupy A B Cv Cven S 0 0 0 0 0 0 0 1 0 1 0 1 0 0 1 0 1 1 1 0 1 0 0 0 1 1 0 1 1 0 1 1 0 1 0 1 1 1 1 1

Doplňky podporující více bitů

Zvlňovač

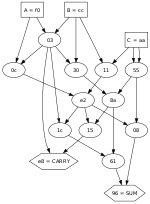

Je možné vytvořit logický obvod pomocí více úplných doplňků k přidání N-bitová čísla. Každý úplný sčítač zadává a Cv, který je Cven předchozí zmije. Tento druh zmije se nazývá a zvlnění (RCA), protože každý nese bit „vlnky“ k dalšímu plnému sčítači. Všimněte si, že první (a pouze první) úplná zmije může být nahrazena poloviční sčítačkou (za předpokladu, že Cv = 0).

Rozložení zmije s vlnovkou je jednoduché, což umožňuje rychlý čas návrhu; sčítač vlnového přenosu je však relativně pomalý, protože každá plná sčítačka musí počkat, až se bitový nosník vypočítá z předchozí plné sčítačky. The zpoždění brány lze snadno vypočítat kontrolou celého obvodu sčítačky. Každá plná sčítačka vyžaduje tři úrovně logiky. Ve 32bitové sčítací jednotce pro zvlnění je 32 úplných sčítačů, takže kritická cesta (nejhorší případ) je zpoždění 3 (od vstupu k nesení v první sčítači) + 31 × 2 (pro šíření přenášení ve druhém sčítači) = 65 zpoždění brány.[3]Obecná rovnice pro nejhorší zpoždění pro a n-bit sčítač carry-zvlnění, který odpovídá součtu i carry bitům, je

Design se střídavou polaritou přenosu a optimalizovaný AND-OR-Invertovat brány mohou být asi dvakrát rychlejší.[4]

Mějte na paměti hledač

Aby se zkrátila doba výpočtu, inženýři vymysleli rychlejší způsoby přidání dvou binárních čísel pomocí add-lookahead adders (CLA). Fungují vytvořením dvou signálů (P a G) pro každou bitovou pozici, na základě toho, zda se přenos šíří z méně významné bitové pozice (alespoň jeden vstup je 1), generovaný v této bitové pozici (oba vstupy jsou 1), nebo zabitý v této bitové pozici (oba vstupy jsou 0). Většinou, P je jednoduše souhrnný výstup poloviny zmije a G je nosný výstup stejného zmije. Po P a G jsou generovány, jsou vytvořeny nosiče pro každou pozici bitu. Některé pokročilé architektury carry-lookahead jsou Manchester přepravní řetěz, Brent – Kung zmije (BKA),[5] a Kogge – kamenná zmije (KSA).[6][7]

Některé další architektury vícebitových sčítačů rozdělují sčítač na bloky. Je možné měnit délku těchto bloků na základě šíření zpoždění obvodů pro optimalizaci doby výpočtu. Mezi tyto doplňky založené na blocích patří sčítač carry-skip (nebo carry-bypass) který bude určovat P a G hodnoty pro každý blok spíše než pro každý bit a carry-select zmije který předem generuje součet a přenáší hodnoty pro buď možný přenosový vstup (0 nebo 1) do bloku pomocí multiplexerů k výběru příslušného výsledku když přenosový bit je znám.

Kombinací několika doplňků carry-lookahead lze vytvořit i větší doplňky. To lze použít na více úrovních, aby se vytvořily ještě větší doplňky. Například následující sčítač je 64bitový sčítač, který používá čtyři 16bitové CLA se dvěma úrovněmi lookahead přepravní jednotky.

Mezi další vzory zmije patří carry-select zmije, sčítač podmíněné částky, sčítač s přeskočením a nést kompletní zmije.

Ukládejte doplňky

Pokud má sčítací obvod vypočítat součet tří nebo více čísel, může být výhodné nešířit výsledek přenosu. Místo toho se používají sčítače se třemi vstupy, které generují dva výsledky: součet a přenos. Součet a přenos mohou být přiváděny do dvou vstupů následného tříčíselného sčítače, aniž by bylo nutné čekat na šíření signálu přenosu. Po všech fázích přidávání je však nutné ke zkombinování výsledného součtu a výsledků nést konvenční sčítač (například zvlnění nebo vyhledávání).

Kompresory 3: 2

Plnou sčítačku lze zobrazit jako a Ztrátový kompresor 3: 2: sečte tři jednobitové vstupy a vrátí výsledek jako jedno dvoubitové číslo; to znamená, že mapuje 8 vstupních hodnot na 4 výstupní hodnoty. Tak například binární vstup 101 vede k výstupu 1 + 0 + 1 = 10 (desetinné číslo 2). Provedení představuje bit jeden z výsledku, zatímco součet představuje bit nula. Podobně lze poloviční sčítač použít jako a Ztrátový kompresor 2: 2, komprimující čtyři možné vstupy do tří možných výstupů.

Takové kompresory lze použít k urychlení součtu tří nebo více přídavků. Pokud jsou doplňky přesně tři, je rozložení známé jako carry-save zmije. Pokud jsou doplňky čtyři nebo více, je nutná více než jedna vrstva kompresorů a pro obvod existují různé možné konstrukce: nejběžnější jsou Tati a Wallace stromy. Tento druh obvodu se nejvíce používá v multiplikátory, což je důvod, proč jsou tyto obvody známé také jako multiplikátory Dadda a Wallace.

Viz také

- Odečítač

- Elektronický mixér - pro přidání analogových signálů

Reference

- ^ Lancaster, Geoffrey A. (2004). Návrh a vývoj softwaru Excel HSC. Pascal Press. p. 180. ISBN 978-1-74125175-3.

- ^ Mano, M. Morris (1979). Digitální logika a počítačový design. Prentice-Hall. str.119–123. ISBN 978-0-13-214510-7.

- ^ Satpathy, Pinaki (2016). Návrh a implementace Carry Select Adder pomocí T-Spice. Anchor Academic Publishing. p. 22. ISBN 978-3-96067058-2.

- ^ Burgess, Neil (2011). Rychlé zvlnění přenášející v CMOS VLSI se standardními buňkami. 20. IEEE Symposium on Computer Arithmetic. 103–111.

- ^ Brent, Richard Peirce; Kung, Hsiang Te (březen 1982). „Pravidelné rozložení pro paralelní přidávače“. Transakce IEEE na počítačích. C-31 (3): 260–264. doi:10.1109 / TC.1982.1675982. ISSN 0018-9340. S2CID 17348212.

- ^ Kogge, Peter Michael; Stone, Harold S. (srpen 1973). „Paralelní algoritmus pro efektivní řešení obecné třídy rekurentních rovnic“. Transakce IEEE na počítačích. C-22 (8): 786–793. doi:10.1109 / TC.1973.5009159. S2CID 206619926.

- ^ Reynders, Nele; Dehaene, Wim (2015). Návrh velmi nízkého napětí energeticky účinných digitálních obvodů. Série analogových obvodů a zpracování signálu. Analog Circuits And Signal Processing (ACSP) (1. vyd.). Cham, Švýcarsko: Springer International Publishing AG Švýcarsko. doi:10.1007/978-3-319-16136-5. ISBN 978-3-319-16135-8. ISSN 1872-082X. LCCN 2015935431.

Další čtení

- Liu, Tso-Kai; Hohulin, Keith R .; Shiau, Lih-Er; Muroga, Saburo (leden 1974). "Optimální jednobitové full-addery s různými typy bran". Transakce IEEE na počítačích. Bell Laboratories: IEEE. C-23 (1): 63–70. doi:10.1109 / T-C.1974.223778. ISSN 0018-9340. S2CID 7746693.

- Lai, Hung Chi; Muroga, Saburo (září 1979). Msgstr "Minimální binární paralelní sčítače s branami NOR (NAND)". Transakce IEEE na počítačích. IEEE. C-28 (9): 648–659. doi:10.1109 / TC.1979.1675433. S2CID 23026844.

- Medovina, řezbář; Conway, Lynn (1980) [prosinec 1979]. Úvod do systémů VLSI (1. vyd.). Reading, MA, USA: Addison-Wesley. Bibcode:1980aw ... kniha ..... M. ISBN 978-0-20104358-7. Citováno 2018-05-12.

- Davio, Marc; Dechamps, Jean-Pierre; Thayse, André (1983). Digitální systémy s implementací algoritmů (1. vyd.). Výzkumná laboratoř společnosti Philips, Brusel, Belgie: John Wiley & Sons, publikace Wiley-Interscience. ISBN 978-0-471-10413-1. LCCN 82-2710.

externí odkazy

- Hardwarové algoritmy pro aritmetické moduly, obsahuje popis několika rozvržení sčítače s obrázky.

- 8bitový plný sčítač a odečítač, ukázka interaktivního Full Adder zabudovaného v JavaScriptu pouze pro účely učení.

- Interaktivní simulace plného sčítače (vyžaduje Javu), interaktivní okruh Full Adder vytvořený online simulátorem obvodu Teahlab.

- Interaktivní simulace polovičního zmije (vyžaduje Javu), obvod Half Adder postavený na simulátoru obvodu Teahlab.

- 4bitová simulace Full Adder postavený ve Verilogu a doprovodný Výukový program Ripple Carry Full Adder

- Shirriff, Ken (listopad 2020). „Zpětné inženýrství obvodu carry-lookahead v procesoru Intel 8008“.