Xilinx Vivado - Xilinx Vivado

| |

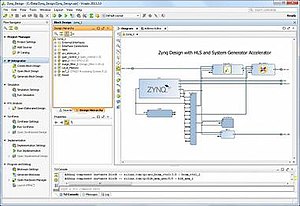

Xilinx Vivado Design Suite 2014.2 s panelem Block Design (uprostřed) a navigačním stromem projektu (vlevo) | |

| Vývojáři | Xilinx |

|---|---|

| První vydání | Duben 2012[1] |

| Stabilní uvolnění | |

| Napsáno | C ++ |

| Operační systém | Microsoft Windows, Linux |

| K dispozici v | Angličtina |

| Typ | EDA |

| Licence | Vydání WebPACK: bez poplatků pro vybraná (menší) zařízení[4] Další vydání: komerční |

| webová stránka | www |

Vivado Design Suite je softwarová sada od společnosti Xilinx pro syntézu a analýzu HDL návrhy, nahrazující Xilinx ISE s dalšími funkcemi pro systém na čipu vývoj a syntéza na vysoké úrovni.[1][5][6][7] Vivado představuje pozemský přepis a přemýšlení o celém toku návrhu (ve srovnání s ISE).[8][9][10]

Stejně jako novější verze ISE, Vivado zahrnuje vestavěný logický simulátor ISIM.[11] Vivado také zavádí syntézu na vysoké úrovni s nástrojovým řetězcem, který převádí C kód do programovatelné logiky.[6]

Výměna 15letého ISE za Vivado Design Suite trvala 1 000 osoboroků a stála 200 milionů USD.[12]

Funkce

Vivado byl představen v dubnu 2012,[1] a je integrovaným návrhovým prostředím (IDE) s nástroji na úrovni systému od IC postavenými na sdíleném škálovatelném datovém modelu a společném ladicím prostředí. Vivado zahrnuje návrhové nástroje na úrovni elektronického systému (ESL) pro syntézu a ověřování algoritmické IP založené na C; standardizované balení algoritmické i RTL IP pro opětovné použití; standardy založené na IP šití a systémové integraci všech typů systémových stavebních bloků; a ověřování bloků a systémů.[13] Bezplatná verze Vivado WebPACK poskytuje designérům omezenou verzi návrhového prostředí.[14]

Součásti

The Syntéza na vysoké úrovni Vivado překladač povoluje C, C ++ a SystemC programy, které mají být přímo zacíleny na zařízení Xilinx, aniž by bylo nutné ručně vytvářet RTL.[15][16][17] Vivado HLS je široce přezkoumáván za účelem zvýšení produktivity vývojářů a je potvrzeno, že podporuje třídy C ++, šablony, funkce a přetížení operátorů.[18][16] Vivado 2014.1 představil podporu automatického převodu OpenCL jádra na IP pro zařízení Xilinx.[19][16] Jádra OpenCL jsou programy, které se spouštějí na různých platformách CPU, GPU a FPGA.[16][19]

The Vivado Simulator je součástí sady Vivado Design Suite. Jedná se o simulátor kompilovaného jazyka, který podporuje smíšený jazyk, Tcl skripty, šifrovaná IP a vylepšené ověření.

The Integrátor Vivado IP umožňuje technikům rychle integrovat a konfigurovat IP z velké knihovny IP Xilinx. Integrátor je také naladěn MathWorks Simulink designy vytvořené pomocí generátoru systému Xilinx a syntézy na vysoké úrovni Vivado.[20]

The Obchod Vivado Tcl je skriptovací systém pro vývoj doplňků k Vivado a lze jej použít k přidání a úpravě schopností Vivado.[19] Tcl je skriptovací jazyk, na kterém je založeno samotné Vivado.[19] Všechny základní funkce Vivado lze vyvolat a ovládat pomocí skriptů Tcl.[19]

Podpora zařízení

Vivado podporuje Xilinx řady 7 a všechna novější zařízení (řady UltraScale a UltraScale +).[3] U vývoje zaměřeného na starší zařízení a CLPD Xilinx již ukončeno Xilinx ISE musí být použito.

Reference

- ^ A b C „Xilinx Inc, Form 8-K, aktuální zpráva, datum podání 25. dubna 2012“. secdatabase.com. Citováno 6. května 2018.

- ^ Vydání Vivado 2020.1, Xilinx

- ^ A b Vivado Design Suite and User Guide, Release Notes, Installation, and Licensing, UG973 (v2020.1), June 3, 2020, Xilinx

- ^ „Vyhodnocení sady Vivado Design Suite a WebPACK“. Xilinx. n.d. Citováno 4. října 2020.

- ^ Morris, Kevi (18. 11. 2014). „FPGA ochladí datové centrum, Xilinx zahřívá závod“. Electronic Engineering Journal.

- ^ A b „Xilinx a jeho ekosystém předvádějí na ISE 2015 všechna programovatelná a chytřejší řešení vidění“. SAN JOSE. 04.02.2015.

- ^ „Sada Xilinx Vivado Design Suite je nyní k dispozici ve verzi WebPACK“. SAN JOSE: Design & Reuse. 19. 12. 2012.

- ^ Morris, Kevin (2014-02-25). „Xilinx vs. Altera, volání akce v největší rivality polovodičů“. Electronic Engineering Journal.

- ^ Vivado Design Suite Web Xilinx

- ^ Vivado Design Suite „První verze vydaná v roce 2012, Xilinx ke stažení

- ^ Funkce Vivado, Xilinx

- ^ Joselyn, Louise (10.12.2013). „Cesta k úspěchu je pro začínající podniky eda dlouhá a těžká“. Nová elektronika.

- ^ EDN. "Sada Vivado Design Suite až čtyřnásobně zrychluje integraci a implementaci programovatelných systémů. “15. června 2012. Citováno 25. června 2013.

- ^ Clive Maxfield, EE Times. "Nyní je k dispozici vydání WebPACK sady Xilinx Vivado Design Suite. “20. prosince 2012. Citováno 25. června 2013.

- ^ Xilinx zvyšuje produktivitu pro všechny programovatelné SoC Zynq-7000 pomocí sady Vivado Design Suite 2014.3, SDK a nového metodického průvodce pro vestavěný design UltraFast, SAN JOSE, 8. října 2014, Design & Reuse

- ^ A b C d „Vivado Design Suite 2014.1 zvyšuje produktivitu automatizací metodiky návrhu UltraFast a hardwarovou akcelerací OpenCL“. SAN JOSE: Sledování trhu. 16. 04. 2014.

- ^ Maxfield, Clive (2013-07-26). „Bezplatný průvodce syntézou na vysoké úrovni pro inženýry S / W“. EE Times.

- ^ Wilson, Richard (2014-05-27). „Jak zajistit, aby pomalý software běžel rychleji“. Týdenní elektronika.

- ^ A b C d E Morris, Kevin (06.05.2014). „Viva Vivado !, nástroje pro vyladění Xilinx“. Electronic Engineering Journal.

- ^ Wilson, Richard (11.9.2013). „Xilinx, MathWorks a National Instruments pracují na návrhu FPGA na vysoké úrovni“. Týdenní elektronika.