Pokročilé rozšiřitelné rozhraní - Advanced eXtensible Interface - Wikipedia

The Pokročilé rozšiřitelné rozhraní (AXI), část PAŽE Pokročilá architektura sběrnice mikrokontroléru 3 (AXI3) a 4 (AXI4) specifikace,[1] je paralelní vysoký výkon, synchronní, vysoká frekvence, multi-master, multi-slave sdělení rozhraní, určený hlavně pro komunikaci na čipu.

Společnost AXI byla představena v roce 2003 se specifikací AMBA3. V roce 2010 definovala nová revize AMBA, AMBA4, AXI4, AXI4-Lite a AXI4-Stream protokol. AXI je bez licenčních poplatků a jeho specifikace je volně dostupná z PAŽE.

AXI nabízí široké spektrum funkcí, včetně:

- samostatný adresa / řídicí a datové fáze

- podpora pro nevyrovnané přístupy k datům

- hromadné přenosy s jediným přenosem spouštění adresa

- samostatné a nezávislé kanály pro čtení a zápis

- podpora nevyřízených transakcí

- podpora dokončování transakcí mimo objednávku pro transakce s různými ID podprocesů na stejném hlavním portu. (Transakce na stejném hlavním portu, které mají stejné ID vlákna, musí být dokončeny v pořadí. Kromě toho mohou být různé hlavní porty dokončeny mimo pořadí, pokud jde o sebe.)

- podpora pro atomové operace.

AMBA AXI specifikuje mnoho volitelných signály, které mohou být volitelně zahrnuty v závislosti na konkrétních požadavcích designu,[2] Díky tomu je AXI univerzální sběrnicí pro mnoho aplikací.

Při komunikaci přes AXI autobus je mezi jedním nadřízeným a jedním podřízeným, specifikace obsahuje podrobný popis a signály zahrnout propojení N: M, schopné rozšířit sběrnici na topologie s více mastery a slave.[3]

AMBA AXI4, AXI4-Lite a AXI4-Stream byly přijaty společností Xilinx a mnoho z jejích partnerů jako hlavní komunikační sběrnice ve svých produktech.[4][5]

ID vláken

ID podprocesů umožňují jednomu hlavnímu portu podporovat více podprocesů, přičemž každé podproces má přístup v pořadí v adresním prostoru AXI, avšak každé ID podprocesu iniciované z jednoho hlavního portu může být vzájemně mimo pořadí dokončeno. Například v případě, že jedno ID vlákna je blokováno pomalou periferií, může pokračovat další ID vlákna nezávisle na pořadí prvního ID vlákna. Dalšímu příkladu může být jednomu vláknu na procesoru přiděleno ID vlákna pro konkrétní přístup do paměti hlavního portu, jako je čtení addr1, zápis addr1, čtení addr1 a tato sekvence bude dokončena v uvedeném pořadí, protože každá transakce má stejné ID vlákna hlavního portu. Jiné vlákno běžící na CPU může mít přiřazeno jiné ID vlákna hlavního portu a jeho přístup do paměti bude také v pořádku, ale možná smíchán s prvními transakcemi ID vlákna.

ID podprocesů na hlavním portu nejsou globálně definována, proto přepínač AXI s více hlavními porty interně předponou index hlavního portu před ID podprocesu a poskytne toto zřetězené ID podprocesu zařízení slave a poté po návratu transakce do jeho hlavní port původu, tato předpona ID vlákna bude použita k vyhledání hlavního portu a předpona bude zkrácena. To je důvod, proč je ID podprocesu slave portu širší v bitech než ID podprocesu hlavního portu.

Sběrnice Axi-lite je sběrnice AXI, která podporuje pouze jeden podproces ID na master. Tato sběrnice se obvykle používá pro koncový bod, který potřebuje komunikaci pouze s jedním hlavním zařízením najednou, například jednoduchou periferní zařízení, jako je UART. Naproti tomu CPU je schopen masteringu na více periferií a adresních prostorů najednou a bude podporovat více než jedno ID vlákna na svých hlavních portech axi a slave portech. To je důvod, proč CPU obvykle podporuje plnou specifickou sběrnici axi. Typický příklad spínače axi na přední straně by zahrnoval plný spec axi master připojený k CPU master a několik axi-lite slave připojených k axi switchi z různých periferních zařízení.

(Dodatečná sběrnice axi-lite je omezena pouze na podporu délek transakcí 1 datového slova na transakci.)

Potřesení rukou

AXI definuje základní mechanismus potřesení rukou složený ze signálů xVALID a xREADY.[6] Signál xVALID je řízen zdrojem, aby informoval cílovou entitu, že užitečné zatížení na kanálu je platné a lze z něj číst hodinový cyklus dále. Podobně je signál xREADY řízen přijímající entitou, aby oznámil, že je připraven přijímat data.

Když jsou signály xVALID i xREADY vysoké současně hodinový cyklus „datová část dat je považována za„ přenesenou “a zdroj může buď poskytnout novou datovou část dat tím, že udrží vysokou hodnotu xVALID, nebo ukončit přenos deaktivací xVALID. Individuální přenos dat, tedy hodinový cyklus, když jsou hodnoty xVALID i xREADY vysoké, se nazývá „beat“.

Pro řízení těchto signálů jsou definována dvě hlavní pravidla:

- Zdroj nesmí čekat na vysokou hodnotu xREADY k prosazení xVALID.

- Po uplatnění musí zdroj udržovat vysokou hodnotu xVALID, dokud nedojde k potřesení rukou.

Díky tomu potřesení rukou mechanismus, zdroj i cíl mohou řídit tok dat a v případě potřeby omezit rychlost.

Kanály

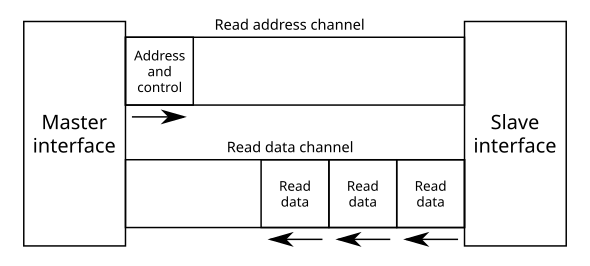

Ve specifikaci AXI pět kanály jsou popsány:[7]

- Přečíst kanál adresy (AR)

- Číst datový kanál (R)

- Kanál pro zápis adresy (AW)

- Zápis datového kanálu (W)

- Kanál odpovědi na zápis (B)

Kromě některých základních pravidel pro objednávání[8] každý kanál je na sobě nezávislý a má svůj vlastní pár xVALID / xREADY potřesení rukou signály.[9]

AXI

Signály

| Popis signálu | Napište kanál adresy | Přečíst kanál adresy |

|---|---|---|

| ID adresy k identifikaci více proudy přes jeden kanál | AWID | ARID |

| Adresa prvního úderu výbuchu | AWADDR | ARADDR |

| Počet úderů uvnitř série | AWLEN[poznámka 1] | ARLEN[poznámka 1] |

| Velikost každého rytmu | Uvědomte si | ARSIZE |

| Typ série | AWBURST | ARBURST |

| Typ zámku, poskytnout atomové operace | AWLOCK[poznámka 1] | ARLOCK[poznámka 1] |

| Typ paměti, jak musí transakce procházet systémem | AWCACHE | ARCACHE |

| Typ ochrany: privilegium, úroveň zabezpečení a přístup k datům / instrukcím | AWPROT | ARPROT |

| Kvalita služeb transakce | AWQOS[pozn. 2] | ARQOS[pozn. 2] |

| Identifikátor oblasti pro přístup k více logickým rozhraním z jednoho fyzického | AWREGION[pozn. 2] | ARREGION[pozn. 2] |

| Uživatelem definovaná data | AWUSER[pozn. 2] | ARUSER[pozn. 2] |

| xVALID potřesení rukou signál | AWVALID | ARVALID |

| xREADY potřesení rukou signál | SKVĚLÉ | PŘIPRAVENO |

| Popis signálu | Zápis datového kanálu | Číst datový kanál |

|---|---|---|

| Data ID, k identifikaci více proudy přes jeden kanál | WID[pozn. 3] | ZBAVIT |

| Čtení / zápis dat | WDATA | RDATA |

| Číst odpověď, chcete-li určit stav aktuálního signálu RDATA | RRESP | |

| Bajtový stroboskop, který označuje, které bajty signálu WDATA jsou platné | WSTRB | |

| Identifikátor posledního rytmu | WLAST | RLAST |

| Uživatelem definovaná data | WUSER[pozn. 2] | RUSER[pozn. 2] |

| xVALID potřesení rukou signál | WVALID | RVALID |

| xREADY potřesení rukou signál | WREADY | OPRAVDU |

| Popis signálu | Napište kanál odpovědi |

|---|---|

| Napište ID odpovědi, abyste identifikovali více proudy přes jeden kanál | NABÍDKA |

| Zapsat odpověď a určit stav shluku | BRESP |

| Uživatelem definovaná data | BUSER[pozn. 2] |

| xVALID potřesení rukou signál | BVALID |

| xREADY potřesení rukou signál | BREADY |

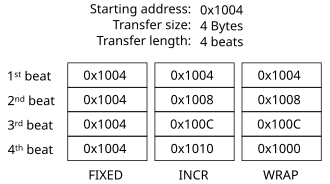

Výbuchy

AXI je založen na sérii protokol,[11] což znamená, že pro jeden požadavek může existovat více datových přenosů (nebo bitů). To je užitečné v případech, kdy je nutné přenést velké množství dat z nebo na konkrétní vzor adres. V AXI mohou být shluky tří typů, vybraných signály ARBURST (pro čtení) nebo AWBURST (pro zápisy) ):[12]

- PEVNÝ

- INCR

- ZABALIT

Ve FIXOVANÝCH dávkách má každý úder v rámci přenosu stejnou adresu. To je užitečné pro opakovaný přístup na stejné místo v paměti, například při čtení nebo zápisu FIFO.

Na druhou stranu v dávkách INCR má každý rytmus adresu rovnající se té předchozí plus velikost přenosu. Tento typ série se běžně používá ke čtení nebo zápisu oblastí sekvenční paměti.

WRAP shluky jsou podobné těm INCR, protože každý přenos má adresu rovnající se předchozímu plus velikost přenosu. Avšak s WRAP shluky, pokud adresa aktuálního rytmu dosáhne "hranice vyšší adresy", je resetována na "hranici zalomení":

s

Transakce

Čte

Chcete-li zahájit transakci čtení, musí master poskytnout na kanálu adresy čtení:

- počáteční adresa na ARADDR

- typ série, FIXOVANÝ, INCR nebo WRAP, na ARBURST (je-li k dispozici)

- délka série na ARLEN (je-li k dispozici).

Další pomocné signály, pokud jsou přítomny, se navíc používají k definování konkrétnějších přenosů.

Po obvyklém handshake ARVALID / ARREADY musí slave na kanálu Read data poskytnout:

- údaje odpovídající zadaným adresám na RDATA

- stav každého rytmu na RRESP

plus jakékoli další volitelné signály. Každý rytmus odezvy slave se provádí handshake RVALID / RREADY a při posledním přenosu musí slave prosadit RLAST, aby informoval, že bez nového požadavku na čtení už nebudou následovat žádné další rytmy.

Píše

Chcete-li zahájit operaci zápisu, musí master poskytnout informace o adrese i data.

Informace o adrese jsou poskytovány přes kanál adresy zápisu podobným způsobem jako operace čtení:

- počáteční adresa musí být uvedena na AWADDR

- typ série, FIXOVANÝ, INCR nebo WRAP, na AWBURST (je-li k dispozici)

- délka série na AWLEN (je-li k dispozici)

a pokud jsou k dispozici, všechny volitelné signály.

Master musí také poskytnout data týkající se zadaných adres na kanálu pro zápis dat:

- údaje na WDATA

- "strobo" bity na WSTRB (pokud jsou k dispozici), které podmíněně označují jednotlivé bajty WDATA jako "platné" nebo "neplatné"

Stejně jako v cestě pro čtení musí být na posledním datovém slově WLAST uplatněn masterem.

Po dokončení obou transakcí musí slave poslat zpět do hlavního stavu stav zápisu přes kanál odezvy na zápis vrácením výsledku přes signál BRESP.

AXI4-Lite

AXI4-Lite je a podmnožina protokolu AXI4, poskytující a jako v registru struktura se sníženými funkcemi a složitostí.[14] Pozoruhodné rozdíly jsou:

- všechny dávky jsou složeny pouze z 1 rytmu

- všechny přístupy k datům využívají plnou šířku datové sběrnice, která může být buď 32 nebo 64 bitů

AXI4-Lite odstraňuje část signálů AXI4, ale u ostatních se řídí specifikací AXI4. Být a podmnožina transakcí AXI4 jsou transakce AXI4-Lite plně kompatibilní se zařízeními AXI4, což umožňuje interoperabilita mezi mastery AXI4-Lite a otroky AXI4 bez další logiky převodu.[15]

Signály

| Napište kanál adresy | Napište datový kanál | Napište kanál odpovědi | Přečíst kanál adresy | Přečíst datový kanál |

|---|---|---|---|---|

| AWVALID | WVALID | BVALID | ARVALID | RVALID |

| SKVĚLÉ | WREADY | BREADY | PŘIPRAVENO | OPRAVDU |

| AWADDR | WDATA | BRESP | ARADDR | RDATA |

| AWPROT | WSTRB | ARPROT | RRESP |

Viz také

- Pokročilá architektura sběrnice mikrokontroléru

- Wishbone (počítačová sběrnice)

- Master / slave (technologie)

Reference

- ^ "AMBA | Dokumentace". Držení paží.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. 109–118. Citováno 5. července 2019.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. str. 23–24. Citováno 5. července 2019.

- ^ „Protokol rozhraní AMBA AXI4“. www.xilinx.com. Xilinx Inc.

- ^ „AXI4 IP“. www.xilinx.com. Xilinx Inc.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. 37–38. Citováno 5. července 2019.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. s. 22–23. Citováno 5. července 2019.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. str. 40. Citováno 5. července 2019.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. str. 38. Citováno 5. července 2019.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. str. 28–34. Citováno 5. července 2019.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. str. 22. Citováno 5. července 2019.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. str. 45–47. Citováno 5. července 2019.

- ^ A b Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. str. 44. Citováno 5. července 2019.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. s. 121–128. Citováno 5. července 2019.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. str. 124. Citováno 5. července 2019.

- ^ Držení paží. „Specifikace protokolu AMBA AXI a ACE“ (PDF). developer.arm.com. str. 122. Citováno 5. července 2019.