Výměna blesku NOR - NOR flash replacement - Wikipedia

Zatímco flash paměť zůstává jedním z nejoblíbenějších úložišť v vestavěné systémy kvůli jeho nestálost, nárazuvzdornost, malá velikost a nízká spotřeba energie, její aplikace výrazně přesáhla svůj původní design. Na základě svého původního designu je flash paměť NOR navržena pro ukládání binárního kódu programů, protože podporuje XIP (eXecute-In-Place) a vysoký výkon při operacích čtení, zatímco paměť NAND flash se používá jako úložiště dat kvůli své nižší ceně a vyššímu výkonu při operacích zápisu a mazání ve srovnání s bleskem NOR. V posledních letech klesla cena blesku NAND mnohem rychleji než cena blesku NOR. Aby se nakonec snížily náklady na hardware, stává se používání NAND flash jako náhrada NOR flash (motivováno silnou poptávkou na trhu) novým trendem v konstrukcích vestavěných systémů, zejména na mobilní telefony a arkádové hry.

Přehled

Výměna závisí na dobře navržené správě flash paměti, kterou provádí buď software na hostitelském systému (jako surové médium), nebo hardwarové obvody / firmware uvnitř jeho zařízení. Zde je navržen efektivní predikční mechanismus s omezenými požadavky na paměťový prostor a efektivní implementací. Mechanismus predikce shromažďuje přístupové vzory provádění programu, aby vytvořil graf predikce přijetím pracovní sada pojem. Podle predikčního grafu předpovědní mechanismus předem načte data (/ kód) do SRAM mezipaměť, aby se snížila míra vynechání mezipaměti. Proto se zlepšuje výkon provádění programu a efektivně se zaplňuje rozdíl ve výkonu čtení mezi NAND a NOR.

Efektivní strategie načítání

Liší se od populárních ukládání do mezipaměti nápady v hierarchie paměti, tento přístup je zaměřen na mechanismus ukládání do mezipaměti orientovaný na aplikace, který na základě daných stop provádění aplikací přijímá předběžné načítání podporované predikcí. Návrhy vestavěných systémů jsou zvažovány s omezenou sadou aplikací, jako je sada vybraných systémových programů v mobilních telefonech nebo arkádové hry strojů zábavních parků. Kromě toho je při implementaci omezena kapacita a výpočetní výkon SRAM.

Hardwarová architektura

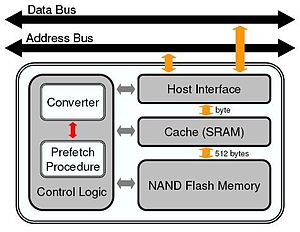

Návrh hardwaru zahrnuje čtyři základní součásti: hostitelské rozhraní, SRAM (mezipaměť), flash paměť NAND a řídicí logika. Za účelem vyplnění mezery ve výkonu mezi NAND a NOR slouží SRAM jako vrstva mezipaměti pro přístup k datům přes NAND. Rozhraní hostitele odpovídá za komunikaci s hostitelským systémem prostřednictvím adresy a dat autobusy. Nejdůležitější je, že řídicí logika spravuje aktivitu ukládání do mezipaměti a poskytuje servisní emulaci NOR flash s NAND flash a SRAM; musí mít implementovaný inteligentní predikční mechanismus ke zlepšení výkonu systému. V řídicí logice existují dvě hlavní součásti: Převodník emuluje přístup NOR flash přes NAND flash s mezipamětí SRAM, kde je nutné překládat adresy z adresování bajtů (pro NOR) do Adresa logického bloku (LBA) adresování (pro NAND). Všimněte si, že každá stránka NAND 512B / 2KB odpovídá jedné, respektive čtyřem LBA. Procedura předběžného načtení se pokusí předem načíst data z NAND na SRAM, takže rychlost přístupu NOR přístupu je přes SRAM vysoká. Postup by měl analyzovat a extrahovat chování cílové aplikace prostřednictvím sady shromážděných stop. Podle extrahovaných vzorů přístupu ze shromážděných tras procedura generuje predikční informace, které se označují jako predikční graf.

Predikční graf

Vzor přístupu provádění aplikace přes NOR (nebo NAND) se skládá ze sekvence LBA. Jelikož aplikace běží několikrát, může se zobrazit „prakticky“ úplný obrázek o možném přístupovém vzoru provádění aplikace. Vzhledem k tomu, že většina spuštění aplikace je závislá na vstupu nebo je řízena daty, může po daném LBA následovat více než jeden následný LBA, kde každý LBA odpovídá jednomu uzlu v grafu. Uzly s více než jedním následným LBA se nazývají větvové uzly a ostatní se nazývají běžné uzly. Graf, který odpovídá vzorům přístupu, se označuje jako predikční graf konkrétní aplikace. Pokud by bylo možné stránky v NAND flash předem načítat včas a je zde dostatek prostoru SRAM pro ukládání do mezipaměti, pak by všechny přístupy k datům mohly být prováděny přes SRAM.

Aby se graf predikce uložil na flash paměť s minimalizací režií (kapacita SRAM), jsou následné informace LBA každého běžného uzlu uloženy do náhradní oblasti odpovídající stránky. Je to proto, že náhradní oblast stránky v současných implementacích má nevyužitý prostor a čtení stránky obvykle přichází se čtením jejích dat a náhradních oblastí současně. Tímto způsobem přístup k následným informacím LBA běžného uzlu přichází bez dalších nákladů. Vzhledem k tomu, že uzel větve má více než jeden následný LBA, nemusí mít volná oblast odpovídající stránky dostatek volného místa pro uložení informací. Udržuje se tedy tabulka větví, aby se uložily následné informace LBA všech uzlů větví. Výchozí vstupní adresu tabulky větví, která odpovídá uzlu větve, lze uložit do náhradní oblasti příslušné stránky. Počáteční položka zaznamenává počet následujících LBA pobočkového uzlu a následné LBA jsou uloženy v položkách následujících po počáteční položce. Tabulku větví lze uložit na flash paměť. Během doba běhu, lze celou tabulku načíst do SRAM pro lepší výkon. Pokud není dostatek místa na paměti SRAM, lze části tabulky načíst do souboru na požádání móda.

Postup předběžného načtení

Cílem postupu předběžného načítání je předběžné načítání dat z NAND na základě daného predikčního grafu tak, aby k většině přístupů k datům došlo přes SRAM. Základní myšlenkou je předběžné načtení dat podle pořadí LBA v grafu. Aby bylo možné efektivně vyhledat vybranou stránku v mezipaměti, a cyklická fronta je přijat ve správě mezipaměti. Data přednastavená z flash NAND jsou načtena, zatímco data přenesená na hostitele jsou na druhou stranu vyřazena. Postup předběžného načtení se provádí v a chamtivý způsob: Nechť P1 bude poslední předem načtená stránka. Pokud P1 odpovídá běžnému uzlu, je předem načtena stránka, která odpovídá následující LBA. Pokud P1 odpovídá uzlu větve, pak by měl postup předběžně načíst stránky sledováním všech možných dalších odkazů LBA ve stejné základně a každý s každým způsob.