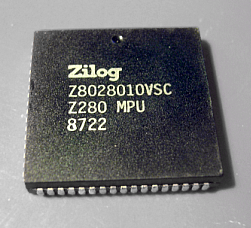

Zilog Z280 - Zilog Z280

The Zilog Z280 je 16-bit mikroprocesor, vylepšení Zilog Z80 architektura, představená v červenci 1987. Je to v zásadě Z800, přejmenován, s mírnými vylepšeními, jako je například výroba v CMOS.[1] Bylo to komerční selhání. Zilog přidal a jednotka správy paměti (MMU) k rozšíření rozsah adresování do 16MB, funkce pro multitasking a víceprocesorový a koprocesor konfigurace a 256 bajtů statické paměti RAM na čipu, konfigurovatelné jako a mezipaměti pro pokyny a / nebo data nebo jako součást běžného adresního prostoru. Má obrovské množství nových instrukce a režimy adresování což dává celkem více než 2000 kombinací. Je schopen efektivně zpracovávat 32bitové datové operace, včetně hardwarového násobení, dělení a rozšíření znaménka. Nabízí provozní režimy Supervisor a User a volitelně oddělené adresní prostory pro instrukce a data v obou režimech (celkem čtyři možné adresní prostory). Je to vnitřní hodinový signál lze nakonfigurovat tak, aby běžely 1, 2 nebo 4násobkem rychlosti externích hodin (napřMHz procesor s 3 MHz autobus ). Na rozdíl od Z80 používá Z280 multiplexované uspořádání adres a datových sběrnic. Úspěšnější rozšíření Z80 -architektura zahrnuje Hitachi HD64180 v roce 1986 a Zilog eZ80 v roce 2001, mimo jiné. Viz dále Zilog Z800.

Z280 měl na svou dobu mnoho pokročilých funkcí, většina z nich se na procesoru Zilog už nikdy nesetkala:

- Pokyny a data na čipu mezipaměti nebo RAM na čipu

- Návod Potrubí

- Vysoce výkonné 16bitové rozhraní Z-BUS nebo 8bitové rozhraní sběrnice kompatibilní se Z80

- Integrovaná MMU s ochrana paměti

- Schopnost určit, která sada registrů je v kontextu s pokyny JAF a JAR

- Čtyři 16bitové čítače / časovače na čipu

- Čtyři na čipu DMA kanály

- Plně duplexní UART na čipu

- Uživatel I / O past

- Režim správce (výsadní instrukce)

- Protiprávní pokyny past

- Koprocesor emulace past

- Přístup do paměti v režimu Burst

- Multiprocesor podpora s mnoha režimy konfigurace sběrnice

- Podpora více externích koprocesorů prostřednictvím zrychleného komunikačního rozhraní

- Více I / O stránek, což také umožňuje interní I / O zařízení bez omezení rozsahu adres I / O portů jako na eZ80 nebo konflikt s existujícími základní deska zařízení, jako je Z180.

- Přetečení zásobníku Varování

Poznámky

Reference

- ^ EDN 27. listopadu 1986, str. 133

- Předběžná technická příručka k mikroprocesorové jednotce Z280 MPU (PDF). San Jose, Kalifornie: Zilog. 1989. Citováno 2009-07-15. (Poznámka: 20 MB soubor PDF)

- Rodinná kniha Z80. San Jose, Kalifornie: Zilog. Leden 1989.

- Reh, Tilmann (1991-09-16). „CPU280 a Z280“. TCJ. Citováno 2009-07-15.

Další čtení

- Harston, J.G. (1998-04-15). „Úplný seznam opcode Z280“. Citováno 2009-07-15.

Tento článek je založen na materiálu převzatém z Zdarma online slovník výpočetní techniky před 1. listopadem 2008 a začleněno pod "licencování" podmínek GFDL, verze 1.3 nebo novější.

| Tento mikropočítač - nebo mikroprocesor související článek je a pahýl. Wikipedii můžete pomoci pomocí rozšiřovat to. |