MIPI Debug Architecture - MIPI Debug Architecture

tento článek příliš spoléhá na Reference na primární zdroje. (Prosince 2018) (Zjistěte, jak a kdy odstranit tuto zprávu šablony) |

MIPI Alliance Debug Architecture poskytuje standardizovanou infrastrukturu pro ladění hluboce vestavěné systémy v mobilním a mobilně ovlivněném prostoru. The Aliance MIPI MIPI Debug Working Group vydala portfolio specifikací; jejich cílem je poskytovat standardní ladicí protokoly a standardní rozhraní z a systém na čipu (SoC) k ladicímu nástroji. Dokument Přehled architektury pro ladění shrnuje veškeré úsilí. V posledních letech se skupina zaměřila na specifikaci protokolů, které zlepšují viditelnost vnitřních operací hluboce zabudovaných systémů, standardizaci řešení ladění prostřednictvím funkčních rozhraní tvarový faktor zařízení a upřesnění použití I3C jako ladicí sběrnice.[1][2]

Termín „debug“

Pojem „ladění“ zahrnuje různé metody používané k detekci, třídění, sledování a potenciální eliminaci chyb nebo chyb v hardwaru a softwaru. Ladění zahrnuje metody řízení / konfigurace, ladění režimu stop / krok a různé formy sledování.

Metody řízení / konfigurace

Debug lze použít k ovládání a konfiguraci komponent daného cílového systému, včetně vestavěných systémů. Standardní funkce zahrnují nastavení hardwaru hraniční body, příprava a konfigurace sledovacího systému a zkoumání systému státy.

Stop / krok ladění režimu

V ladění režimu stop / step je jádro / mikrokontrolér zastaven pomocí zarážek a poté "jednostupňový" prostřednictvím kódu prováděním pokynů po jednom. Pokud ostatní jádra / mikrokontroléry SoC skončily synchronně, lze zkoumat celkový stav systému. Ladění režimu stop / krok zahrnuje techniky řízení / konfigurace, řízení běhu jádra / mikrokontroléru, synchronizaci start / stop s jinými jádry, přístup k paměti a registru a další funkce ladění, jako je čítač výkonu a přístup do paměti za běhu.

Trasování

Stopy umožňují hloubkovou analýzu chování a časových charakteristik zabudovaného systému. Typické jsou následující stopy:

- „Trasování jádra“ poskytuje plnou viditelnost provádění programu na vloženém jádru. Trasovací data se vytvářejí pro sekvenci provádění instrukcí (někdy označovanou jako trasování instrukce) a datové přenosy (někdy označované jako trasování dat). SoC může generovat několik hlavních stop.

- „Trasování sběrnice“ poskytuje úplnou viditelnost datových přenosů přes konkrétní sběrnici.

- „Trasování systému“ poskytuje viditelnost různých událostí / stavů uvnitř zabudovaného systému. Stopová data lze generovat kódem aplikace přístroje a hardwarovými moduly v rámci SoC. SoC může generovat několik trasování systému.

Viditelnost interních operací SoC

Trasování je nástrojem volby pro monitorování a analýzu toho, co se děje v komplexním SoC. Existuje několik dobře zavedených standardů non-MIPI core-trace a bus-trace pro vložený trh. Pracovní skupina pro ladění MIPI tedy nemusela specifikovat nové. Když však pracovní skupina pro ladění zveřejnila svou první verzi systému, neexistoval žádný standard pro "trasování systému" Trasovací protokol systému MIPI (MIPI STP) v roce 2006.

Trasování systémového softwaru MIPI (MIPI SyS-T)

Generování dat trasování systému ze softwaru se obvykle provádí vložením dalších volání funkcí, která vytvářejí diagnostické informace cenné pro proces ladění. Tato technika ladění se nazývá instrumentace. Příklady jsou: funkce generující řetězec ve stylu printf, informace o hodnotě, tvrzení atd. Účel Trasování systémového softwaru MIPI (MIPI SyS-T) je definovat opakovaně použitelný univerzální datový protokol a přístrojové vybavení API pro ladění. Specifikace definuje formáty zpráv, které umožňují nástroji pro trasovací analýzu dekódovat debugovací zprávy, ať už na text čitelný člověkem, nebo na signály optimalizované pro automatickou analýzu.

Vzhledem k tomu, že podrobné textové zprávy omezují při ladění omezení šířky pásma, jsou k dispozici takzvané „katalogové zprávy“. Zprávy z katalogu jsou kompaktní binární zprávy, které nahrazují řetězce číselnými hodnotami. Překlad z číselné hodnoty na řetězec zprávy se provádí nástrojem pro stopovou analýzu pomocí kolaterálu XML informace. Tyto informace jsou poskytovány během procesu vytváření softwaru pomocí schématu XML, který je také součástí specifikace.

Datový protokol SyS-T je navržen tak, aby efektivně fungoval na dopravních spojích nižší úrovně, jako jsou ty definované v Trasovací protokol systému MIPI. Funkce protokolu SyS-T, jako je časové razítko nebo kontrolní součet integrity dat, lze deaktivovat, pokud takové možnosti již poskytuje dopravní spojení. Využití dalších dopravních spojů - například UART, USB nebo TCP / IP —Je také možné.

Pracovní skupina MIPI Debug poskytne referenční implementaci open-source pro instrumentační API SyS-T, tiskárnu zpráv SyS-T a nástroj pro generování dat XML zajištění, jakmile Specifikace pro trasování systémového softwaru (SyS-T) je schválen.[3]

Trasovací protokol systému MIPI (MIPI STP)

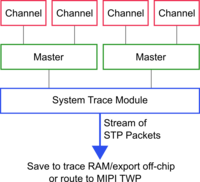

The Trasovací protokol systému MIPI (MIPI STP) určuje obecný protokol, který umožňuje sloučení trasovacích proudů pocházejících z libovolného místa v SoC do sledovacího proudu 4bitových rámců. Byl záměrně navržen tak, aby slučoval informace o trasování systému. The Trasovací protokol systému MIPI používá topologii kanálu / hlavní jednotky, která umožňuje analytickému nástroji pro příjem trasování shromažďovat jednotlivé sledovací proudy pro analýzu a zobrazení. Protokol dále poskytuje následující funkce: synchronizace a zarovnání streamu, značky spouštění, globální časové razítko a synchronizace času s více streamy.

Proud paketů STP produkovaný sledovacím modulem systému lze přímo uložit ke sledování RAM, přímo exportovat mimo čip nebo jej lze směrovat do modulu „protokol protokolu obálky“ (TWP) a sloučit s dalšími sledovacími proudy. PAŽE CoreSight System Trace Macrocell,[4] který je v souladu s MIPI STP, je dnes nedílnou součástí většiny vícejádrových čipů používaných v mobilním prostoru.

Poslední verze MIPI přijatá deskou Specifikace pro System Trace Protocol (STPSM) je verze 2.2 (únor 2016).[5]

Protokol MIPI Trace Wrapper Protocol (MIPI TWP)

The Protokol MIPI Trace Wrapper Protocol umožňuje sloučit více sledovacích proudů do jednoho sledovacího proudu (bajtové proudy). Každému sledovacímu proudu je přiřazovacím protokolem přiřazeno jedinečné ID. Detekce hranic bajtů / slov je možná, i když jsou data přenášena jako proud bitů. Inertní pakety se používají, pokud je vyžadován nepřetržitý export trasovacích dat. Protokol MIPI Trace Wrapper Protocol je založen na ARM Protokol trasovacího formátovače specifikováno pro ARM CoreSight.

Poslední verze MIPI přijatá deskou Specifikace protokolu Trace Wrapper Protocol (TWPSM) je verze 1.1 (prosinec 2014).[6]

Od vyhrazených po funkční rozhraní

Vyhrazená ladicí rozhraní

V raných fázích vývoje produktu je běžné používat vývojové desky s vyhrazenými a snadno přístupnými ladicími rozhraními pro připojení ladicích nástrojů. SoC používané na mobilním trhu se spoléhají na dvě technologie ladění: ladění v zastaveném režimu pomocí řetězce skenování a ladění v zastavovacím režimu prostřednictvím ladicích registrů mapovaných v paměti.

Následující standardy pro ladění jiné než MIPI jsou na zavedeném trhu dobře zavedené: IEEE 1149.1 (5kolíkový) a ARM Serial Wire Debug (2kolíkové), oba využívající jednostranné piny. Není tedy nutné, aby pracovní skupina pro ladění MIPI určovala ladicí protokol v zastavovacím režimu nebo určovala ladicí rozhraní.

Sledovací data generovaná a sloučená do sledovacího proudu v rámci SoC lze streamovat prostřednictvím vyhrazeného jednosměrného sledovacího rozhraní, mimo čip do nástroje pro trasovací analýzu. MIPI Debug Architecture poskytuje specifikace pro paralelní i sériové porty trasování.

The Rozhraní paralelního trasování MIPI (MIPI PTI) určuje, jak předat sledovací data více datovým pinům a hodinovému kolíku (s jedním koncem). Specifikace zahrnuje názvy a funkce signálů, časování a elektrická omezení. Poslední verze MIPI přijatá deskou Specifikace pro paralelní sledovací rozhraní je verze 2.0 (říjen 2011).[7]

The Vysokorychlostní sledovací rozhraní MIPI (MIPI HTI) určuje, jak streamovat sledovací data přes fyzickou vrstvu standardních rozhraní, jako je PCI Express, DisplayPort, HDMI nebo USB. Aktuální verze specifikace umožňuje jeden až šest jízdních pruhů. Specifikace zahrnuje:

- Vrstva PHY, která představuje elektrickou a taktovací charakteristiku sériových drah.

- Vrstva LINK, která definuje, jak je stopa zabalena do Aurory 8B / 10B protokol.

- Programátorský model pro ovládání HTI a poskytování informací o stavu.

HTI je podmnožinou souboru Vysokorychlostní sériový sledovací port (HSSTP) specifikace definovaná ARM.[8] Poslední verze MIPI přijatá deskou Specifikace vysokorychlostního sledovacího rozhraní je verze 1.0 (červenec 2016).[9]

Vývojáři desek a prodejci ladicích nástrojů těží ze standardních konektorů ladění a standardních mapování pinů. The Doporučení MIPI pro ladicí a trasovací konektory doporučuje 10/20/34 / 34kolíkové konektory na úrovni desky 1,27 milimetru (0,050 palce) (MIPI10 / 20/34). Bylo zadáno sedm různých mapování pinů, které řeší širokou škálu scénářů ladění. Zahrnují standardní JTAG (IEEE 1149.1), cJTAG (IEEE 1149.7) a 4bitová paralelní sledovací rozhraní (používají se hlavně pro trasování systému), doplněná standardem ARD-specific Serial Wire Debug (SWD).[10] Ladicí konektory MIPI10 / 20/34 se staly standardem pro vestavěné designy založené na ARM.

Mnoho vestavěných designů v mobilním prostoru používá vysokorychlostní porty paralelního trasování (až 600 megabitů za sekundu na pin). Společnost MIPI doporučuje 60kolíkový konektor Samtec QSH / QTH s názvem MIPI60, který umožňuje řízení běhu JTAG / cJTAG, až 40 signálů sledovacích dat a až 4 sledovací hodiny. Aby se minimalizovala složitost, doporučení definuje čtyři standardní konfigurace s jedním, dvěma, třemi nebo čtyřmi trasovacími kanály různé šířky.

Poslední verze MIPI přijatá deskou Doporučení MIPI Alliance pro ladicí a trasovací konektory je verze 1.1 (březen 2011).[11]

PHY a pin překrývající rozhraní

Snadno dostupná ladicí rozhraní nejsou ve finálním provedení produktu k dispozici. To brání identifikaci chyb a optimalizaci výkonu v konečném produktu. Vzhledem k tomu, že logika ladění je stále přítomna v koncovém produktu, je nutná alternativní přístupová cesta. Účinným způsobem je vybavit standardní rozhraní mobilního terminálu multiplexorem, který umožňuje přístup k logice ladění. Přepínání mezi základní funkcí rozhraní a funkcí ladění lze iniciovat připojeným ladicím nástrojem nebo softwarem mobilního terminálu. Standardní ladicí nástroje lze použít za následujících podmínek:

- Přepínací protokol je implementován na ladicím nástroji a v mobilním terminálu.

- Existuje ladicí adaptér, který připojuje ladicí nástroj ke standardnímu rozhraní. Ladicí adaptér musí v případě potřeby pomoci přepínacímu protokolu.

- Je zadáno mapování ze standardních kolíků rozhraní na kolíky ladění.

The Úzké rozhraní MIPI pro ladění a testování (MIPI NIDnT) pokryje ladění prostřednictvím následujících standardních rozhraní:microSD, USB 2.0 Micro-B / -AB zásuvka, USB Type-C zásuvka, a DisplayPort. Poslední verze MIPI přijatá deskou Specifikace pro úzké rozhraní pro ladění a testování (NIDnTSM) je verze 1.2 (prosinec 2017).[12]

Síťová rozhraní

Namísto opětovného použití pinů lze ladění provést také pomocí zásobníku protokolu standardního rozhraní nebo sítě. Zde ladicí provoz koexistuje s provozem jiných aplikací využívajících stejné komunikační spojení. Pracovní skupina pro ladění MIPI pojmenovala tento přístup GigaBit Debug. Protože pro tento přístup neexistoval žádný ladicí protokol, pracovní skupina pro ladění MIPI specifikovala svůj ladicí protokol SneakPeak.

Protokol MIPI SneakPeek (MIPI SPP) přesunut z vyhrazeného rozhraní pro základní ladění směrem k rozhraní založenému na protokolu:

- Převádí příchozí pakety příkazů na přístupy pro čtení / zápis do paměti, debugové registry mapované do paměti a další systémové prostředky mapované do paměti.

- Převádí výsledky příkazů (informace o stavu a načtená data pocházející z paměti, registry ladění mapované do paměti a další systémové prostředky mapované do paměti) do odchozích paketů odpovědí.

- Vzhledem k tomu, že SneakPeek přijímá pakety přicházející přes vstupní vyrovnávací paměť a dodává pakety přes výstupní vyrovnávací paměť, lze jej snadno připojit k jakémukoli standardnímu I / O nebo síti.

The Specifikace aliance MIPI pro protokol SneakPeek popisuje základní pojmy, požadovanou infrastrukturu, pakety a datový tok. Poslední verze MIPI přijatá deskou Specifikace protokolu SneakPeek (SPPSM) je verze 1.0 (srpen 2015).[13]

The Rodina specifikací gigabitového ladění MIPI poskytuje podrobnosti pro mapování ladicích a trasovacích protokolů na standardní I / O nebo sítě dostupné v mobilních terminálech. Mezi tyto podrobnosti patří: adresování koncových bodů, inicializace a správa odkazů, balení dat, správa toku dat a detekce a obnovení chyb. Poslední verze MIPI přijatá deskou Specifikace pro Gigabit Debug pro USB (MIPI GbD USB) je verze 1.1 (březen 2018).[14] Poslední verze MIPI přijatá deskou Specifikace pro Gigabit Debug pro zásuvky internetového protokolu (MIPI GbD IPS) je verze 1.0 (červenec 2016).[15]

I3C jako ladicí sběrnice

Aktuální řešení ladění, jako jsou JTAG a ARM CoreSight, jsou staticky strukturovaná, což umožňuje omezenou škálovatelnost, pokud jde o přístupnost ladicích komponent / zařízení. Ladění MIPI pro I3C určuje škálovatelné dvoukolíkové ladicí řešení s jedním koncem, jehož výhodou je, že je k dispozici po celou dobu životnosti produktu. Sběrnici I3C lze použít pouze jako ladicí sběrnici, nebo ji lze sdílet mezi laděním a její základní funkcí jako sběrnice sběru dat pro senzory. Ladění přes I3C funguje v zásadě následovně:

- Sběrnice I3C se používá pro fyzický přenos a nativní funkce I3C se používá ke konfiguraci sběrnice ak připojení nových komponent za provozu.

- Debugovací protokol je zabalen do vyhrazených příkazů I3C. Podporované protokoly ladění jsou JTAG, ARM CoreSight a protokol MIPI SneakPeek.[13]

Reference

- ^ „Pracovní skupina pro ladění“. Aliance MIPI. 2019. Citováno 7. června 2019.

- ^ "Přehled architektury pro ladění" (PDF). Aliance MIPI. Verze 1.2. 13. července 2018. Citováno 7. června 2019.

- ^ „Systémový software MIPI - Trace (MIPI SyS-T)“. Aliance MIPI. Verze 1.0. Dubna 2018. Citováno 7. června 2019.

- ^ „System Trace Macrocell“. ARM vývojář. 2019. Citováno 7. června 2019.

- ^ „Trasovací protokol systému MIPI (MIPI STP)“. Aliance MIPI. Verze 2.2. Únor 2016. Citováno 7. června 2019.

- ^ „Protokol MIPI Trace Wrapper Protocol (MIPI TWP)“. Aliance MIPI. Verze 1.1. Prosince 2014. Citováno 7. června 2019.

- ^ „Paralelní sledovací rozhraní MIPI (MIPI PTI)“. Aliance MIPI. Verze 2.0. Říjen 2011. Citováno 8. června 2019.

- ^ „CoreSight Architecture Overview: High Speed Serial Trace Port (HSSPT)“. ARM vývojář. 2019. Citováno 8. června 2019.

- ^ „Vysokorychlostní sledovací rozhraní MIPI (MIPI HTI)“. Aliance MIPI. Verze 1.0. Červenec 2016. Citováno 8. června 2019.

- ^ „Serial Wire Debug“. ARM vývojář. 2019. Citováno 8. června 2019.

- ^ „Doporučení MIPI Alliance pro ladicí a sledovací konektory“. Aliance MIPI.

- ^ „Úzké rozhraní MIPI pro ladění a testování (MIPI NIDnT)“. Aliance MIPI. Verze 1.2. Prosince 2017. Citováno 9. června 2019.

- ^ A b „Protokol MIPI SneakPeek (MIPI SPP)“. Aliance MIPI. Verze 1.0. Srpna 2015. Citováno 9. června 2019.

- ^ „MIPI Gigabit Debug pro USB (MIPI GbD USB)“. Aliance MIPI. Verze 1.1. Březen 2018. Citováno 9. června 2019.

- ^ „MIPI Gigabit Debug pro IP zásuvky (MIPI GbD IPS)“. Aliance MIPI. Verze 1.0. Červenec 2016. Citováno 9. června 2019.

externí odkazy

- Schulz, Norbert (Intel Corporation) (26. září 2016). Jak mi specifikace MIPI Debug pomáhají vyvíjet systémový SW. MIPI DevCon 2016. Citováno 9. června 2019.