Minerální syntéza necitlivá na zpoždění - Delay-insensitive minterm synthesis

tento článek poskytuje nedostatečný kontext osobám, které toto téma neznají. (Březen 2012) (Zjistěte, jak a kdy odstranit tuto zprávu šablony) |

DIMS (syntéza mintermů necitlivá na zpoždění) Systém[1] je metodika asynchronního návrhu, která vytváří nejméně možné předpoklady načasování. Za předpokladu pouze necitlivý na kvazi zpoždění zpožďovací model generované designy potřebují malé, pokud vůbec nějaké testování načasování nebezpečí. Základem pro DIMS je použití dvou vodičů k reprezentaci každého bitu dat. Toto se nazývá a dvoukolejná kódování dat. Části systému komunikují brzy čtyřfázový asynchronní protokol.

Konstrukce logických bran DIMS zahrnuje generování všech možných minterm pomocí řady C-prvky a poté shromáždit výstupy z nich pomocí NEBO brány které generují pravdivé a nepravdivé výstupní signály. Se dvěma vstupy se dvěma kolejnicemi by brána byla složena ze čtyř dvou vstupních C prvků. Tři vstupní brány používají osm tří vstupních C prvků.

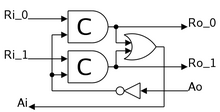

Západky jsou konstruovány pomocí dvou prvků C pro ukládání dat a brány OR pro potvrzení vstupu, jakmile byla data zajištěna připojením datových výstupních vodičů jako jeho vstupů. Potvrzení z dopředného stupně je invertováno a předáno C-prvkům, které jim umožní resetovat po dokončení výpočtu. Tento design západky je známý jako „poloviční západka“. jiný asynchronní západky poskytují vyšší kapacitu dat a úrovně oddělení.

Vzory DIMS jsou velké a pomalé, ale mají tu výhodu, že jsou velmi robustní.

- ^ D. E. Muller, „Asynchronní logika a aplikace na zpracování informací,“ Proc. Symp. Aplikace teorie přepínání ve vesmírné technologii, H. Aiken a W. F. Main, Ed. 289-297, 1963.

Další čtení

- Jens Sparsø, Steve Furber: „Principy návrhu asynchronního obvodu“; Kluwer, Dordrecht (2001); kapitola 5.5.1. ISBN 0-7923-7613-7