Cyrix 6x86 - Cyrix 6x86

Tento článek obsahuje seznam obecných Reference, ale zůstává z velké části neověřený, protože postrádá dostatečné odpovídající vložené citace. (Září 2011) (Zjistěte, jak a kdy odstranit tuto zprávu šablony) |

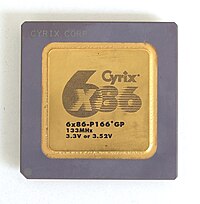

Procesor Cyrix 6x86-P166 | |

| Mezipaměti | |

|---|---|

| L1 mezipaměti | 16 KB (6x86 / L) nebo 64 KB (6x86MX / MII) |

| Architektura a klasifikace | |

| Mikroarchitektura | 6x86 |

| Sada instrukcí | IA-32 /x86 |

| Fyzické specifikace | |

| Tranzistory |

|

| Jádra |

|

| Zásuvka (y) | |

| Produkty, modely, varianty | |

| Model (y) |

|

| Dějiny | |

| Předchůdce | Cyrix Cx486 |

The Cyrix 6x86 (kódové označení M1) je šestá generace, 32-bit x86 mikroprocesor navrhl Cyrix a vyrábí IBM a SGS-Thomson. To bylo původně vydáno v roce 1996.

Architektura

6x86 je superskalární a superpipelovaný a vystupuje přejmenování registrace, spekulativní provedení, provedení mimo objednávku, a závislost na datech odstranění.[1] Nadále však používalo nativní spuštění x86 a běžné mikrokód jen, jako Kentaur je Winchip, na rozdíl od konkurence Intel a AMD který zavedl metodu dynamický překlad do mikro-operace s Pentium Pro a K5. 6x86 je zásuvka -kompatibilní s Intel P54C Pentium, a byl nabízen v šesti výkonnostních úrovních: PR 90+, PR 120+, PR 133+, PR 150+, PR 166+ a PR 200+. Tyto úrovně výkonu se nemapují na rychlost hodin samotného čipu (například PR 133+ běžel na 110 MHz, PR 166+ běžel na 133 MHz atd.).

Pokud jde o vnitřní mezipaměti, má 16-KB hlavní mezipaměti a vedle primární mezipaměti, která funguje jako primární mezipaměť instrukcí, je zahrnuta plně asociativní 256bitová mezipaměť instrukčního řádku.[1]

Modely 6x86 a 6x86L nebyly zcela kompatibilní s Intel P5 Pentium instrukční sada a není schopen pracovat s více procesory. Z tohoto důvodu se čip identifikoval jako a 80486 a deaktivoval CPUID instrukce ve výchozím nastavení. Podporu CPUID lze povolit nejprve povolením rozšířených registrů CCR a poté nastavením bitu 7 v CCR4. Nedostatek plné kompatibility P5 Pentium způsobil problémy s některými aplikacemi, protože programátoři začali používat pokyny specifické pro P5 Pentium. Některé společnosti vydaly opravy svých produktů, aby fungovaly na 6x86.

Kompatibilita s Pentiem byla vylepšena u modelu 6x86MX přidáním a Počítadlo časových razítek na podporu instrukce RDTSC P5 Pentium.[2] Byla přidána také podpora instrukcí CMOVcc Pentium Pro.[2]

Výkon

Podobně jako AMD s jejich K5 a brzy K6 procesory, Cyrix použil a Hodnocení PR (Performance Rating), aby vztahovali svůj výkon k Intel P5 Pentium (před-P55C ), protože vyšší výkon 6x86 za hodinu ve srovnání s P5 Pentium lze vyčíslit oproti vyšší taktované části Pentia. Například, 133 MHz 6x86 bude odpovídat nebo překonávat P5 Pentium na 166 MHz, a ve výsledku by Cyrix mohl prodávat 133 MHz čip jako P5 Pentium 166. Hodnocení PR však nebylo zcela pravdivým vyjádřením výkonu modelu 6x86.

Zatímco celočíselný výkon modelu 6x86 byl výrazně vyšší než výkon P5 Pentium, jeho výkon s plovoucí desetinnou čárkou byl průměrnější - mezi 2 a 4násobkem výkonu 486 FPU za taktovací cyklus (v závislosti na provozu a přesnosti). The FPU v 6x86 byl do značné míry stejný obvod, který byl vyvinut pro dřívější vysoce výkonné koprocesory kompatibilní s 8087/80287/80387 kompatibilní s Cyrix, který byl na svou dobu velmi rychlý - Cyrix FPU byl mnohem rychlejší než 80387, a dokonce i 80486 FPU. Stále to však bylo podstatně pomalejší než nové a zcela přepracované P5 Pentium a P6 Pentium Pro -Pentium III FPU.

Během vývoje modelu 6x86 byla většina aplikací (kancelářský software stejně jako hry) prováděly téměř výhradně celočíselné operace. Designéři předvídali, že budoucí aplikace si toto zaměření výuky s největší pravděpodobností udrží. Abychom tedy optimalizovali výkon čipu pro to, co považovali za nejpravděpodobnější aplikaci CPU, prostředky pro celočíselné provádění obdržely většinu rozpočtu tranzistoru. To se později ukázalo jako strategická chyba, protože popularita P5 Pentium způsobila mnoho vývojáři softwaru ručně optimalizovat kód montážní jazyk, abyste mohli využít výhod FPU P5 Pentium s pevnou pipeline a nižší latencí. Například velmi očekávané střílečka z pohledu první osoby Zemětřesení použil vysoce optimalizovaný montážní kód navržený téměř výhradně kolem FPU P5 Pentium. Výsledkem je, že P5 Pentium výrazně předčil ostatní CPU ve hře.

Proto, i když byly velmi rychlé hodiny po hodině, byly 6x86 a MII nuceny soutěžit na low-end trhu jako AMD K6 a Intel P6 Pentium II byli vždy napřed v rychlosti hodin. Jednotka s plovoucí desetinnou čárkou „třídy 486“ 6x86 a MII v kombinaci s celočíselnou částí, která byla přinejlepším srovnatelná s novějšími čipy P6 a K6, znamenala, že Cyrix již nemohl konkurovat výkonem.

Modely

6x86

The 6x86 (kódové označení M1) bylo vydáno Cyrix v roce 1996. První generace 6x86 měla problémy s teplem. To bylo primárně způsobeno jejich vyšším tepelným výkonem než jiné denní procesory x86 a jako takoví výrobci počítačů je někdy nevybavili odpovídajícím chlazením. CPU dosáhly vrcholu kolem 25Ž tepelný výkon (jako AMD K6 ), zatímco P5 Pentium vyprodukovalo přibližně 15 W. odpadní teplo na svém vrcholu. Obě čísla by však byla zlomkem tepla generovaného mnoha vysoce výkonnými procesory, o několik let později.

Early Cyrix 6x86 (M1) die shot

6x86L

The 6x86L (kódové označení M1L) byl později propuštěn Cyrix řešit problémy s teplem; the L stojící za nízký výkon. Vylepšené výrobní technologie povolily použití nižšího Vcore. Stejně jako Pentium MMX, 6x86L vyžadoval dělený regulátor napětí v letadle se samostatným napětím pro I / O a jádro CPU.

Cyrix 6x86L (M1L) die shot

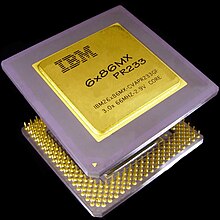

6x86MX / MII

Další vydání 6x86, 6x86MX, přidané MMX kompatibilita spolu s EMMI instrukční sada, vylepšená kompatibilita s Pentium a Pentium Pro přidáním a Počítadlo časových razítek instrukce CMOVcc a čtyřnásobně velikost primární mezipaměti na 64 KB. Mezipaměť řádku 256bajtových instrukčních řádků lze změnit na a mezipaměť zápisníku poskytovat podporu pro multimediální operace.[2] Pozdější revize tohoto čipu byly přejmenovány MII, abychom lépe konkurovali procesoru Pentium II. Bohužel 6x86MX / MII byl pozdě na trh a nemohl dobře měřit rychlost hodin s výrobními procesy používanými v té době.

Cyrix 6x86MX 150 MHz

IBM 6x86MX 133MHz

Cyrix MII 250 MHz

Cyrix 6x86MX (M2) die shot

Reference

- ^ A b "Datový list Cyrix M1" (PDF).

- ^ A b C „Datasheet IBM 6x86MX“ (PDF).

Další čtení

- Gwennap, Linley (25. října 1993). „Cyrix popisuje konkurenta Pentium“ Zpráva mikroprocesoru.

- Gwennap, Linley (5. prosince 1994). "Cyrix M1 Design Tapes Out". Zpráva mikroprocesoru.

- Gwennap, Linley (2. června 1997). „Cyrix 6x68MX překonává AMD K6“. Zpráva mikroprocesoru.

- Slater, Michael (12. února 1996). „Cyrix, IBM Push 6x86 až 133 MHz“. Zpráva mikroprocesoru.

- Slater, Michael (28. října 1996). "Cyrix zdvojnásobuje výkon x86 s M2". Zpráva mikroprocesoru.

externí odkazy

- Cyrix 6x86 ("M1") na PCGuide na Wayback Machine (archivováno 22. června 2017)

- Cyrix 6x86 ("M1") na PCGuide

- cpu-collection.de Obrázky a popisy procesorů Cyrix 6x86

- Porovnání procesorů x86 od Paul Hsieh x86 hloubková analýza procesorů x86 6. generace, včetně 6x86MX.

- Statistiky Cyrix M1 na Sandpile.org